ETHERNET COMMUNICATION MODULE

TX Stall Buffer Descriptor Pointer register

322 Hardware Reference NS9215

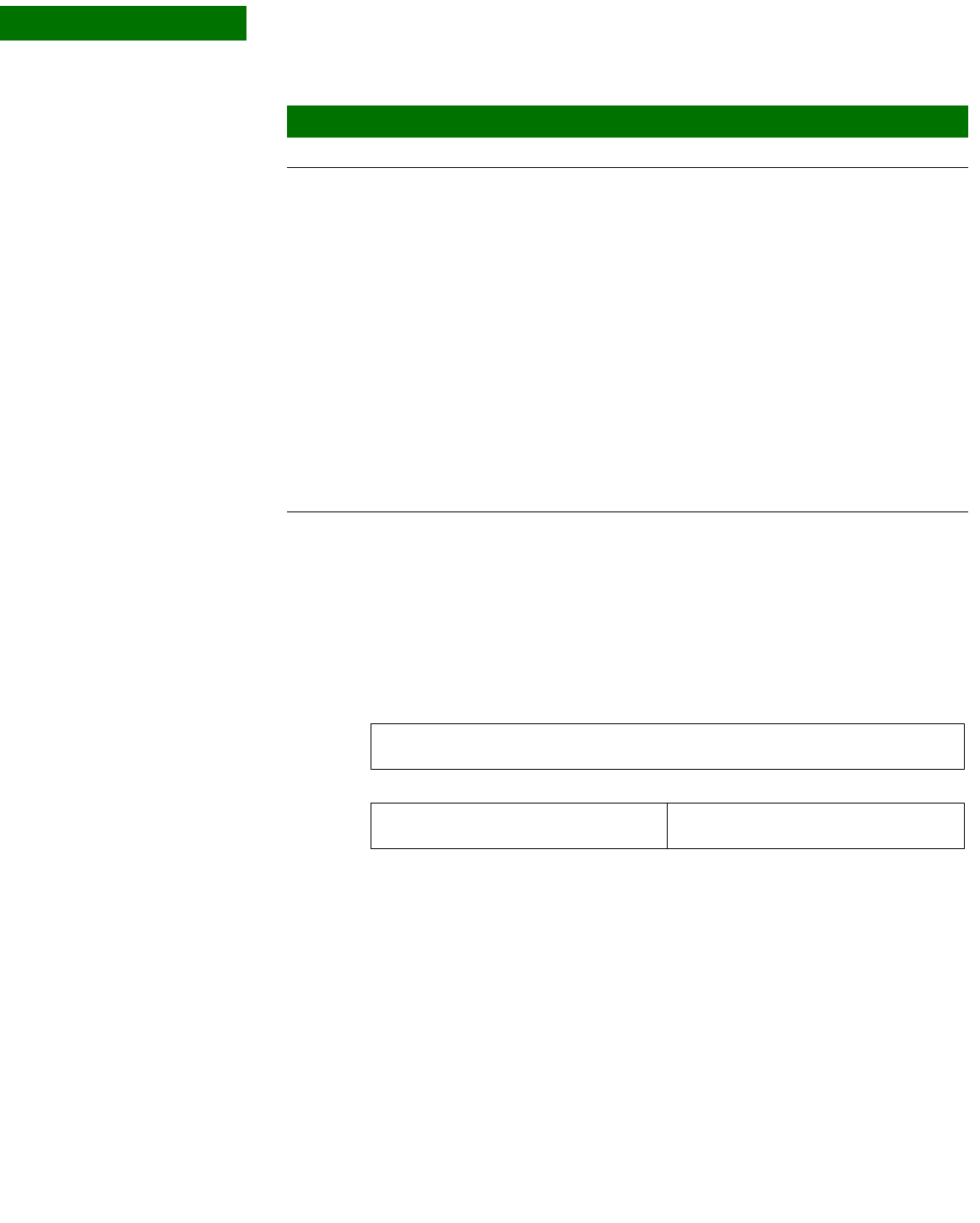

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TX Stall Buffer Descriptor Pointer register

Address: A060 0A24

Register

Bits Access Mnemonic Reset Description

D31:08 N/A Reserved N/A N/A

D07:00 R TXERBD 0x00 Contains the pointer (in the TX buffer descriptor RAM)

to the last buffer descriptor of a frame that was not

successfully transmitted. TXERBD is loaded by the

TX_WR logic when a transmit frame is aborted by the

MAC or when the MAC finds a CRC error in a frame.

TXERBD also is loaded if a buffer descriptor that is not

the first buffer descriptor in a frame does not have its F bit

set.

Note: This pointer is the 8-bit physical address of the

TX buffer descriptor RAM, and points to the

first location of the four-location buffer

descriptor. The byte offset of this buffer

descriptor can be calculated by multiplying this

value by 4.

Note: Software uses TXERBD to identify frames that

were not transmitted successfully.

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved

Reserved

TXSPTR