. . . . .

I/O HUB MODULE

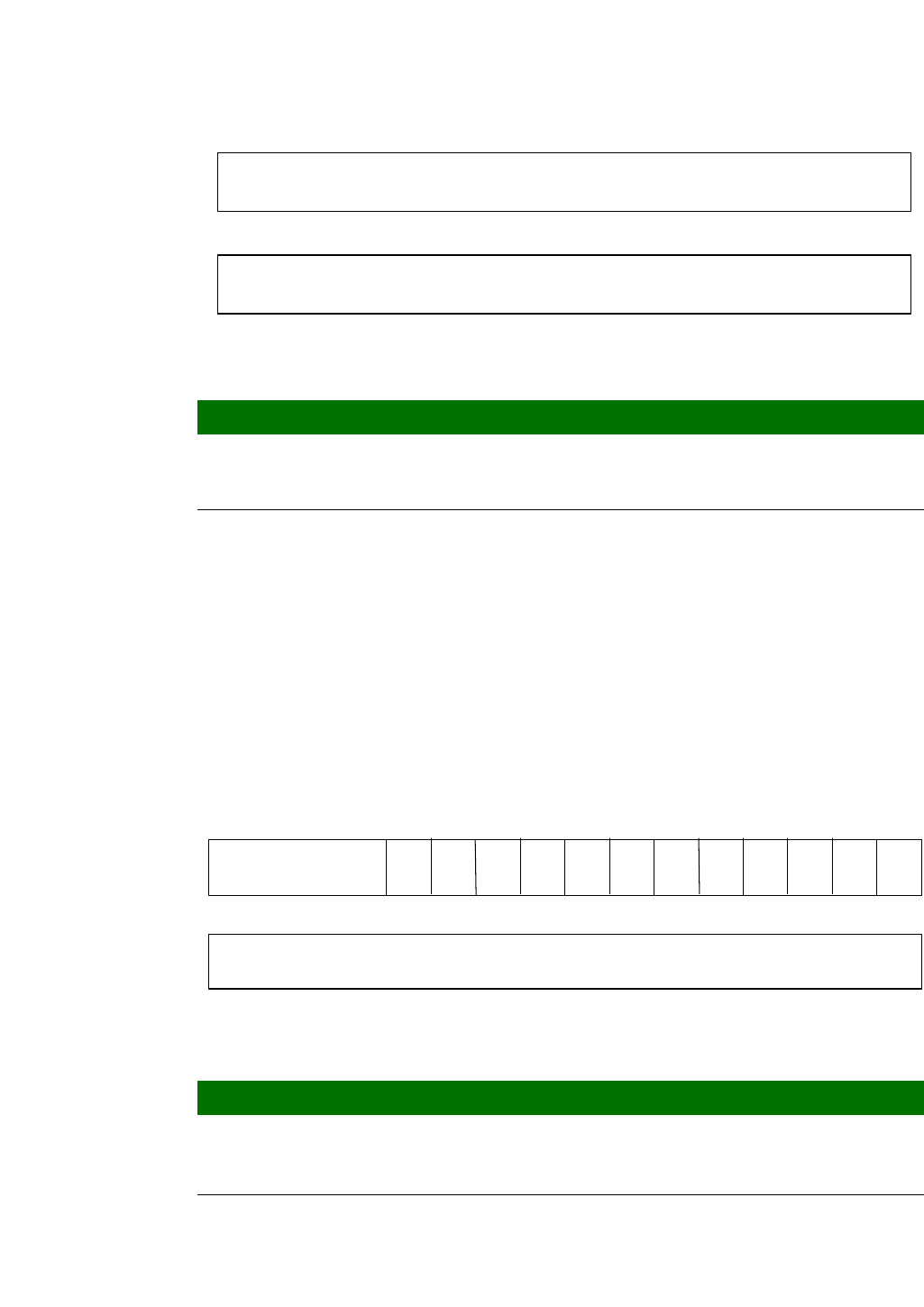

[Module] RX Interrupt Configuration register

www.digiembedded.com 377

Register

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

[ Module] RX Interrupt Configuration register

Addresses: 9000_000C / 9000_800C / 9001_000C / 9001_800C / 9002_000C /

9002_800C / 9003_000C / 9000_800C

The RX Interrupt Configuration register allows system software to configure the

interrupt for the I/O hub module receive channel.

Register

Register bit

assignment

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

RXBDP

RXBDP

Bit(s) Access Mnemonic Reset Description

D31:00 R/W RXBDP 0x0 The first buffer descriptor in the ring. Used when

the W bit is found, which indicates the last buffer

descriptor in the list.

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

BLENSTAT

RXTHRS

Reser

ved

RXFOFIE RXNCIE RXPCIE WSTAT LSTATISTATRXFSRIE RXECIE RXNRIE RXCAIE FSTAT

Bit(s) Access Mnemonic Reset Description

D31:28 R/W RXTHRS 0xF RX FIFO threshold

An interrupt is generated when the FIFO level

rises above this level.

D27 N/A Reserved N/A N/A