. . . . .

TIMING

Clock timing

www.digiembedded.com 511

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Clock timing

All AC characteristics are measured with 10pF, unless otherwise noted.

System PLL

reference clock

timing

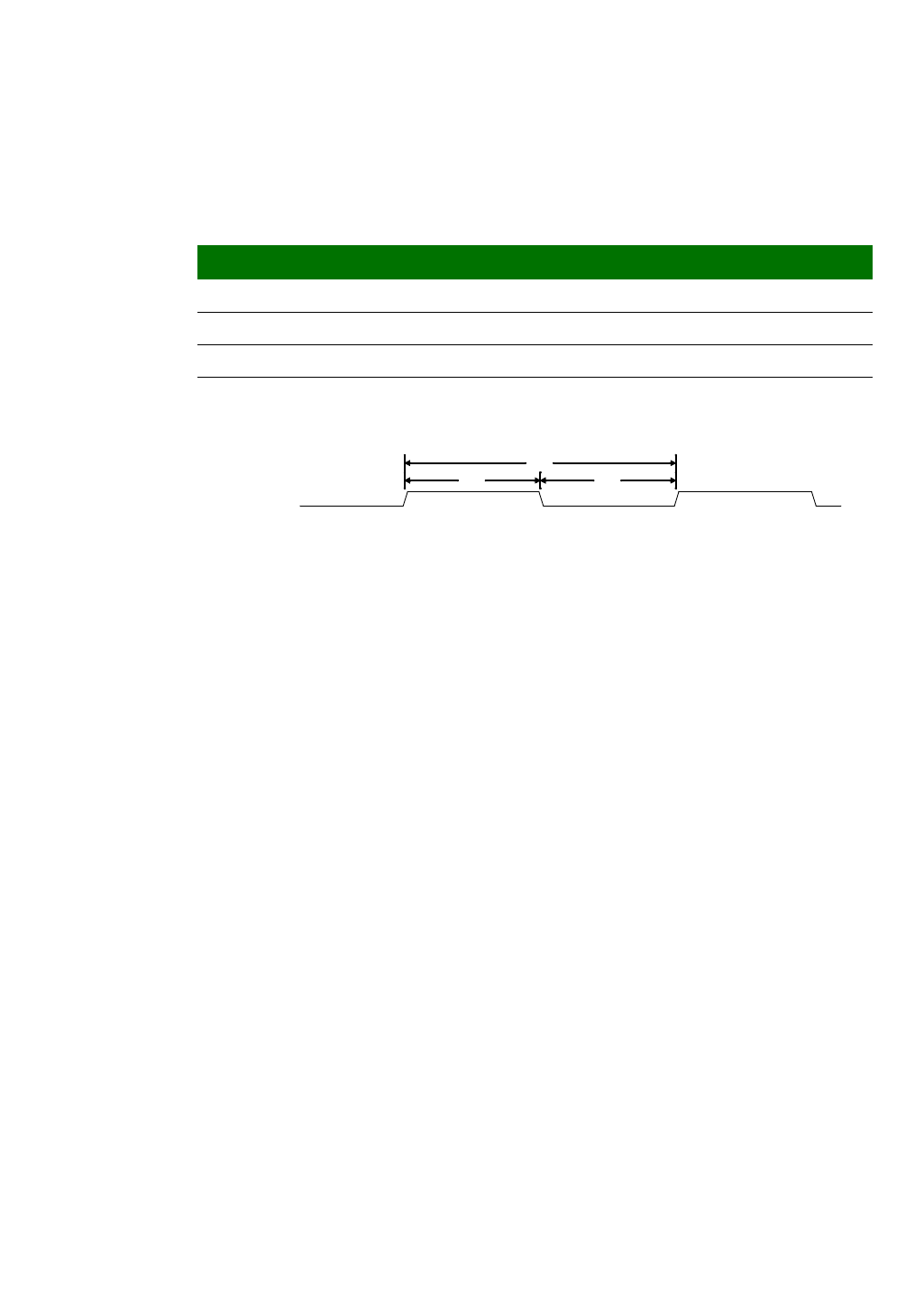

The diagram below pertains to clock timing.

Parm Description Min Max Unit Notes

SC1 x1_sys_osc cycle time 25 50 ns

SC2 x1_sys_osc high time (SC1/2) x 0.45 (SC1/2) x 0.55 ns

SC3 x1_sys_osc low time (SC1/2) x 0.45 (SC1/2) x 0.55 ns

SC1

SC2SC2 SC3

SC1

SC3

x1_sys_osc