WORKING WITH THE CPU

System control processor (CP15) registers

84 Hardware Reference NS9215

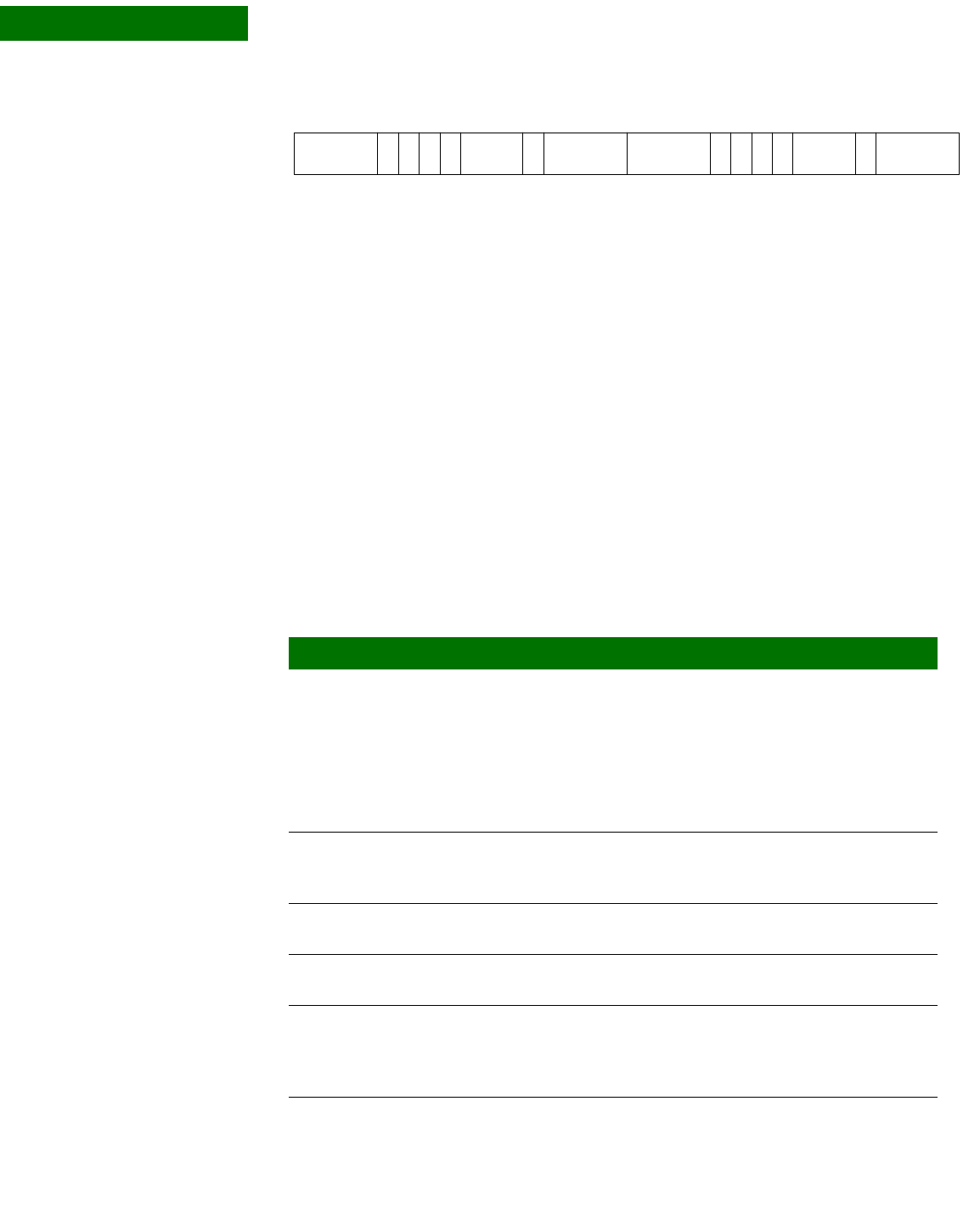

Figure 1: CP15 MRC and MCR bit pattern

The mnemonics for these instructions are:

MCR{cond} p15,opcode_1,Rd,CRn,CRm,opcode_2

MRC{cond} p15,opcode_1,Rd,CRn,CRm,opcode_2

If you try to read from a write-only register or write to a read-only register, you will

have

UNPREDICTABLE results. In all instructions that access CP15:

The opcode_1 field SHOULD BE ZERO, except when the values specified are used

to select the operations you want. Using other values results in unpredictable

behavior.

The opcode_2 and CRm fields SHOULD BE ZERO, except when the values specified

are used to select the behavior you want. Using other values results in

unpredictable behavior.

Terms and

abbreviations

This table lists the terms and abbreviations used in the CP15 registers and

explanations.

Cond

1110 1111 1L

Opcode

_1

Opcode

_2

CRn CRmRd

31 28 27 26 25 24 23 21 20 19 16 15 12 11 10 9 8 7 5 4 3 0

Term Abbreviation Description

UNPREDICTABLE UNP For reads:

The data returned when reading from this location is

unpredictable, and can have any value.

For writes:

Writing to this location causes unpredictable

behavior, or an unpredictable change in device

configuration.

UNDEFINED UND An instruction that accesses CP15 in the manner

indicated takes the

UNDEFINED instruction

exception.

SHOULD BE ZERO SBZ When writing to this field, all bits of the field

SHOULD BE ZERO.

SHOULD BE ONE SBO When writing to this location, all bits in this field

SHOULD BE ONE.

SHOULD BE ZERO or

PRESERVED

SBZP When writing to this location, all bits of this field

SHOULD BE ZERO or PRESERVED by writing the

same value that has been read previously from the

same field.