. . . . .

SERIAL CONTROL MODULE: HDLC

Receive and transmit operations

www.digiembedded.com 415

Serial Control Module: HDLC

CHAPTER 11

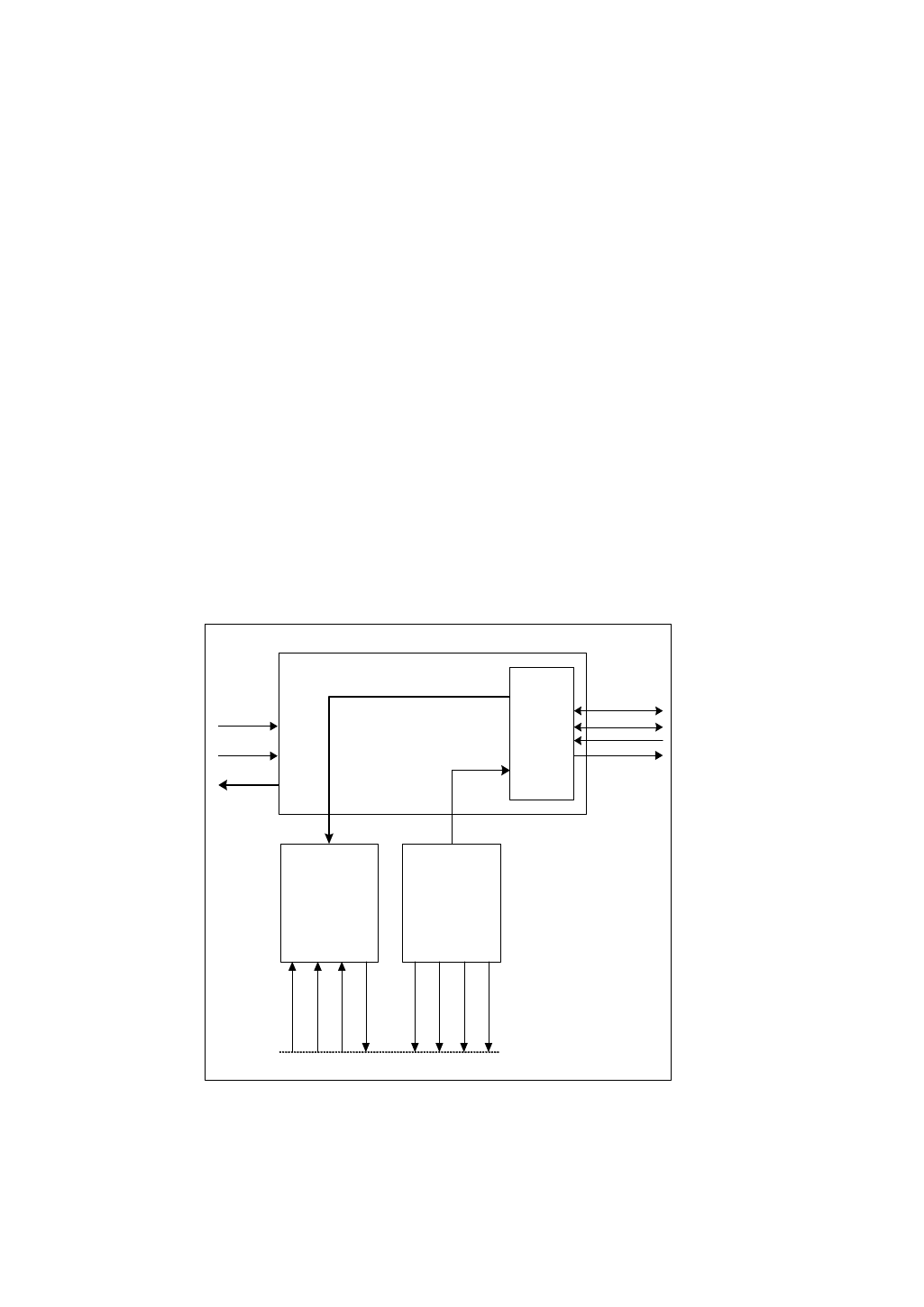

The HDLC module allows full-duplex synchronous communication. Both the

receiver and transmitter can select either an internal or external clock. The HDLC

module encapsulates data within opening and closing flags, and sixteen bits of CRC

precedes the closing flag. All information between the opening and closing flag is

zero-stuffed; that is, if five consecutive ones occur, independent of byte

boundaries, a zero is automatically inserted by the transmitter and automatically

deleted by the receiver. This allows a flag byte (07Eh) to be unique within a serial

stream. The standard CRC-CCITT polynomial

(x16 + x12 + x5 + 1) is implemented, with

the generator and checker preset to all ones.

HDLC module

structure

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receive and transmit operations

Both receive and transmit operations are essentially automatic.

Receive

FIFO

Interface

Transmit

FIFO

Interface

Wrapper

be[1:0]

data[31:0]

read

write

be[1:0]

data[31:0]

status[6:0]

AHB Bus

ref_clk

valid

int

HDLC

RCLK

TXD

RXD

IO Hub

TCLK