WORKING WITH THE CPU

R7:Cache Operations register

96 Hardware Reference NS9215

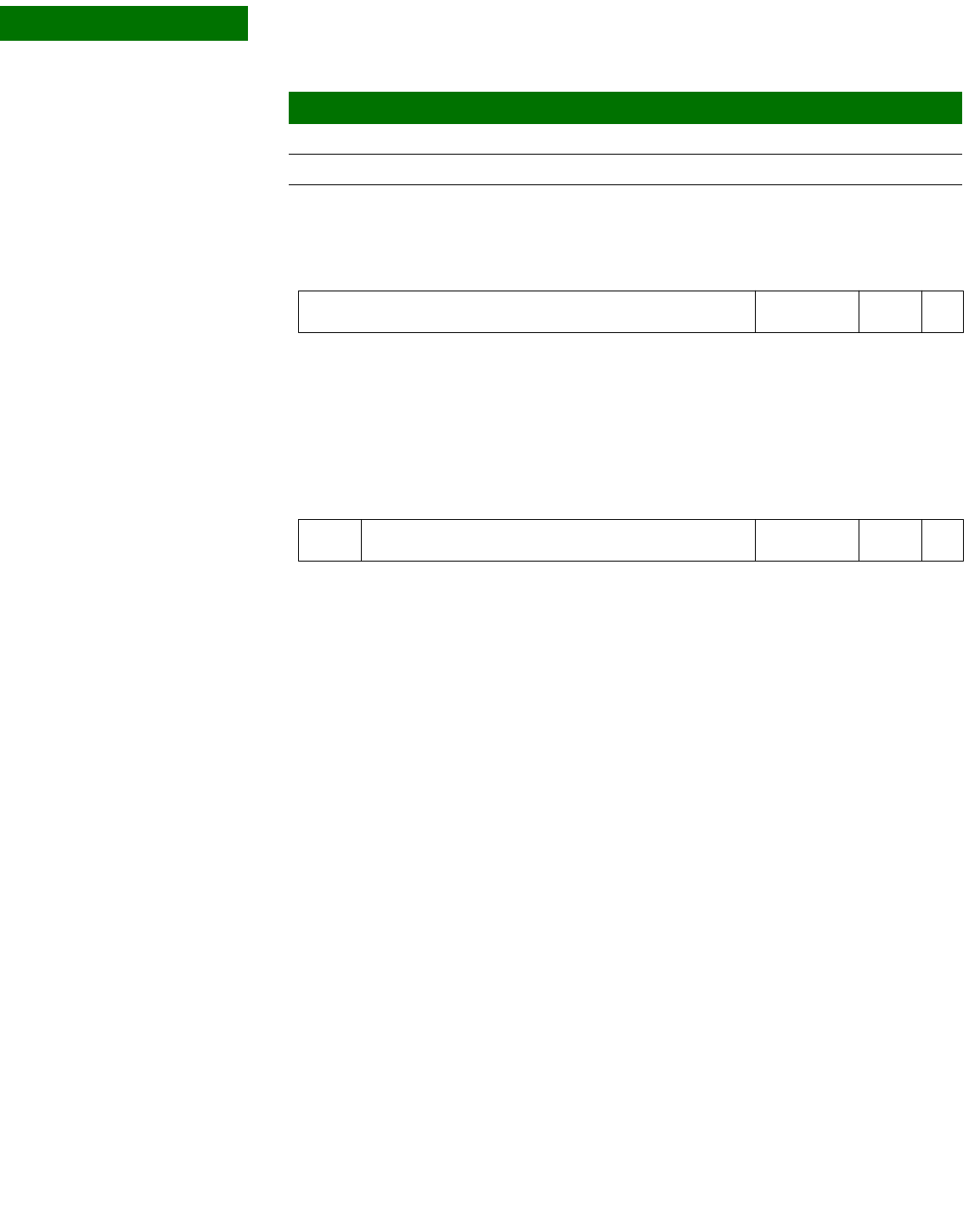

Modified virtual

address format

(MVA)

This is the modified virtual address format for

Rd for the CP15 R7 MCR operations.

The tag, set, and word fields define the MVA.

For all cache operations, the word field SHOULD BE ZERO.

Set/Way format This is the Set/Way format for

Rd for the CP15 R7 MCR operations.

A and S are the base-two logarithms of the associativity and the number of

sets.

The set, way, and word files define the format.

For all of the cache operations, word SHOULD BE ZERO.

Set/Way example For example, a 16 KB cache, 4-way set associative, 8-word line results in the

following:

A = log

2

associativity = log

2

4 = 2

S = log

2

NSETS where

NSETS = cache size in bytes/associativity/line length in bytes:

NSETS = 16384/4/32 = 128

Result: S = log

2

128 = 7

Test and clean

DCache

instructions

The test and clean DCache instruction provides an efficient way to clean the entire

DCache, using a simple loop. The test and clean DCache instruction tests a number

of lines in the DCache to determine whether any of them are dirty. If any dirty lines

are found, one of those lines is cleaned. The test and clean DCache instruction also

returns the status of the entire DCache in bit 30.

Drain write buffer SBZ

MCR p15, 0, Rd, c7, c10, 4

Wait for interrupt SBZ

MCR p15, 0, Rd, c7, c0, 4

Function/operation Data format Instruction

31 0S+4 4

SBZSet(=index) Word

Tag

215S+5

31 0S+4 4

SBZSet(=index) Word

SBZ

215S+5

Way

32-A 31-A