. . . . .

SERIAL CONTROL MODULE: UART

Receive Character-Based Flow Control register

www.digiembedded.com 401

Caution:

Be aware that if multiple matches occur, an XOFF assertion will supersede an

XON assertion.

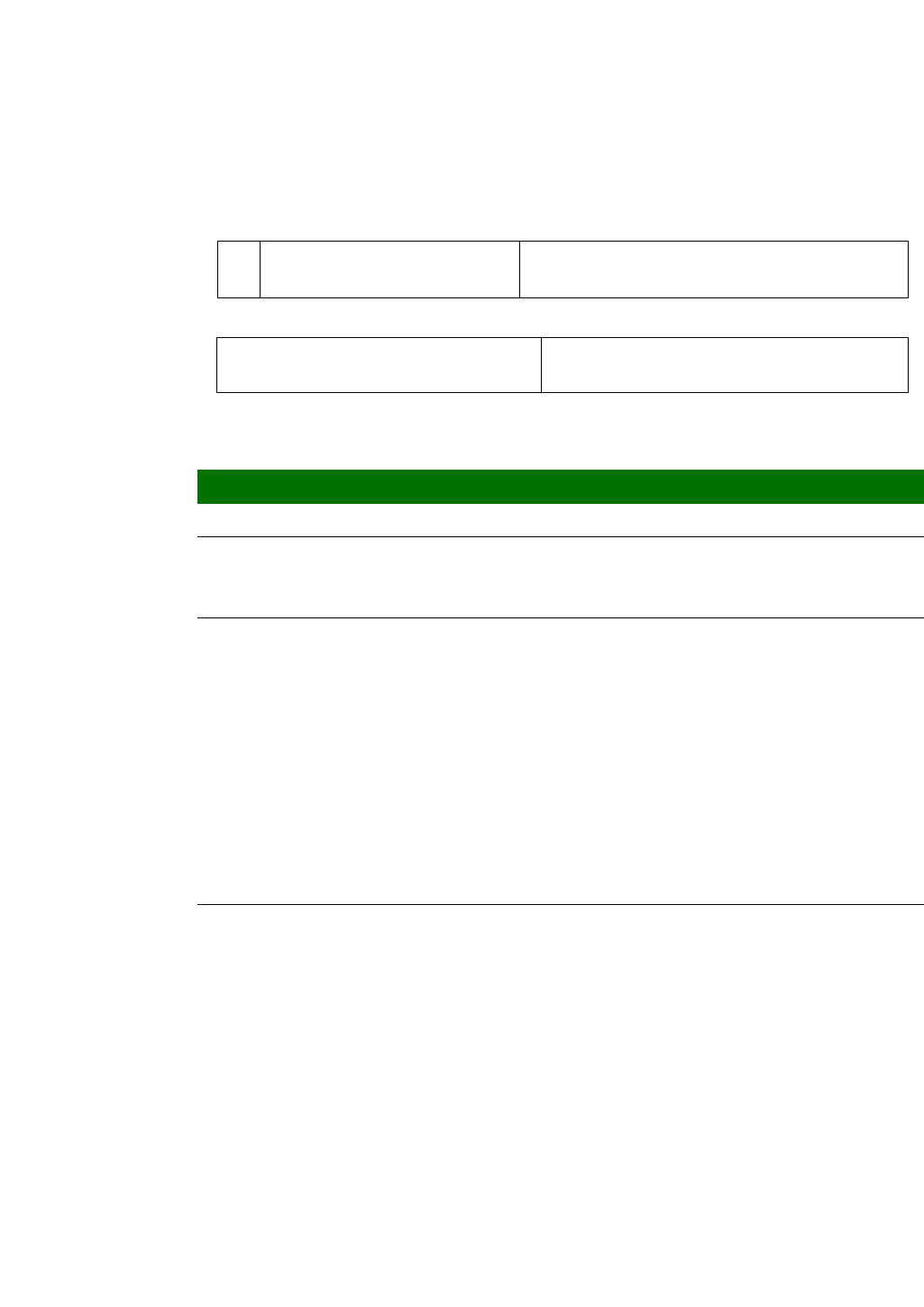

Register

Register bit

assignment

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

EN

ABLE

Not used MASK

Not used

DATA

Bits Access Mnemonic Reset Description

D31:11 R Not used 0 Write this field to 0.

D10 R FLOW_STATE 0x0 Flow control state

0 Hardware initiated XON

1 Hardware initiated XOFF

D09:08 R/W FLOW4 0 Flow control enable

Allows you to define flow characteristics using the

DATA and MASK fields on the Receive Character

Match Control Register 4.

Note: The ENABLE field has no effect on the

flow control logic.

The flow control is defined as shown:

0x Disabled

10 Change the FLOW_STATE field to XON upon

match

11 Change the FLOW_STATE field to XOFF upon

match

D07:06 R/W FLOW3 0 Flow control enable

Allows you to define flow characteristics using the

DATA and MASK fields on the Receive Character

Match Control Register 3.

Note: The ENABLE field has no effect on the

flow control logic.

The flow control is defined as shown:

0x Disabled

10 Change the FLOW_STATE field to XON upon

match

11 Change the FLOW_STATE field to XOFF upon

match