. . . . .

SYSTEM CONTROL MODULE

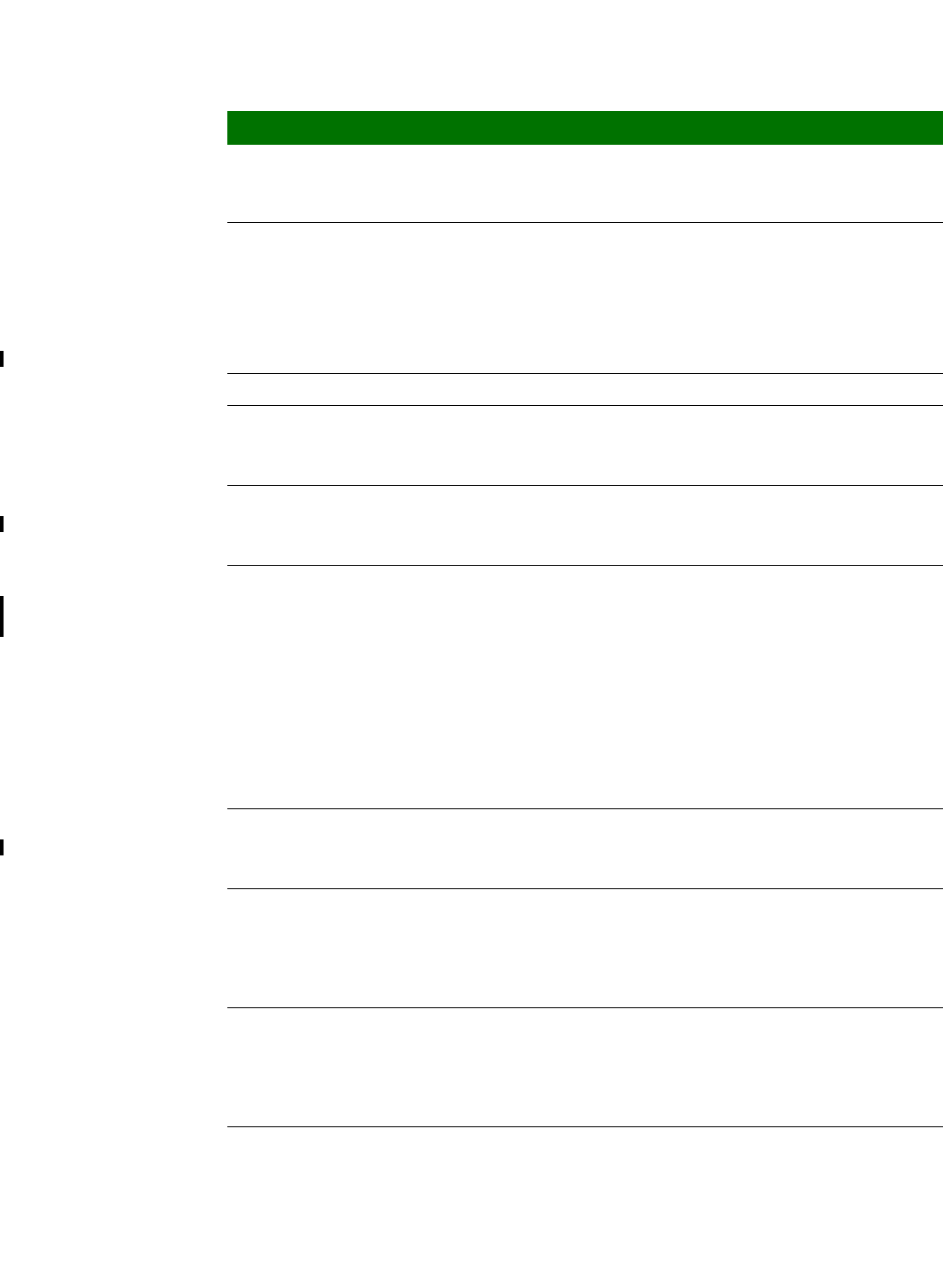

Miscellaneous System Configuration and Status register

www.digiembedded.com 185

Register bit

assignment

Bits Access Mnemonic Reset Description

D31:24 R REV 0x0 Revision

Indicates the hardware identification and revision of

the processor chip.

D23:16 R ID 0x3 Identification

Identifies the chip as:

0 NS9750B-A1

1 NS9360

2 NS9210

3 NS9215

D15:07 N/A Reserved N/A N/A

D06 R AUX/COMP N/A Auxiliary analog comparator status

0 Level is below 2.4V

1 Level is above 2.4V

D05 R Boot mode HW strap

gpio_a[2]

Boot mode

0 Boot from SPI

1 Boot from flash

D04:03 R Boot width HW strap

gpio_a[0]

addr[23]

If boot mode is set to boot from flash:

00 8-bit

01 32-bit

10 32-bit

11 16-bit

If boot mode is set to boot from SPI:

00 Reserved

01 Boot using 8-bit address SPI device

10 Boot using 24-bit address SPI device

11 Boot using 16-bit address SPI device

D02 R/W End mode HW strap

gpio_a[3]

Endian mode

0 Little endian mode

1 Big endian mode

D01 R/W Mis bus resp 0x0 Misaligned bus address response mode

0 Allow misaligned bus addresses

1 Generate an error response when a misaligned

bus address is found; that is, when

haddr bits 1 or

0 are not level 0.

D00 R/W Int reg acc 0x1 Internal register access mode bit 0

0 Allow access to internal registers using

PRIVILEGED mode only

1 Allow access to internal registers using

PRIVILEGED or USER mode