EXTERNAL DMA

Peripheral REQ and DONE signaling

344 Hardware Reference NS9215

Determining the

width of PDEN

Use the memory controller’s Static Memory Write Delay register and Static Memory

Write Enable Delay register to determine the width of the PDEN assertion.

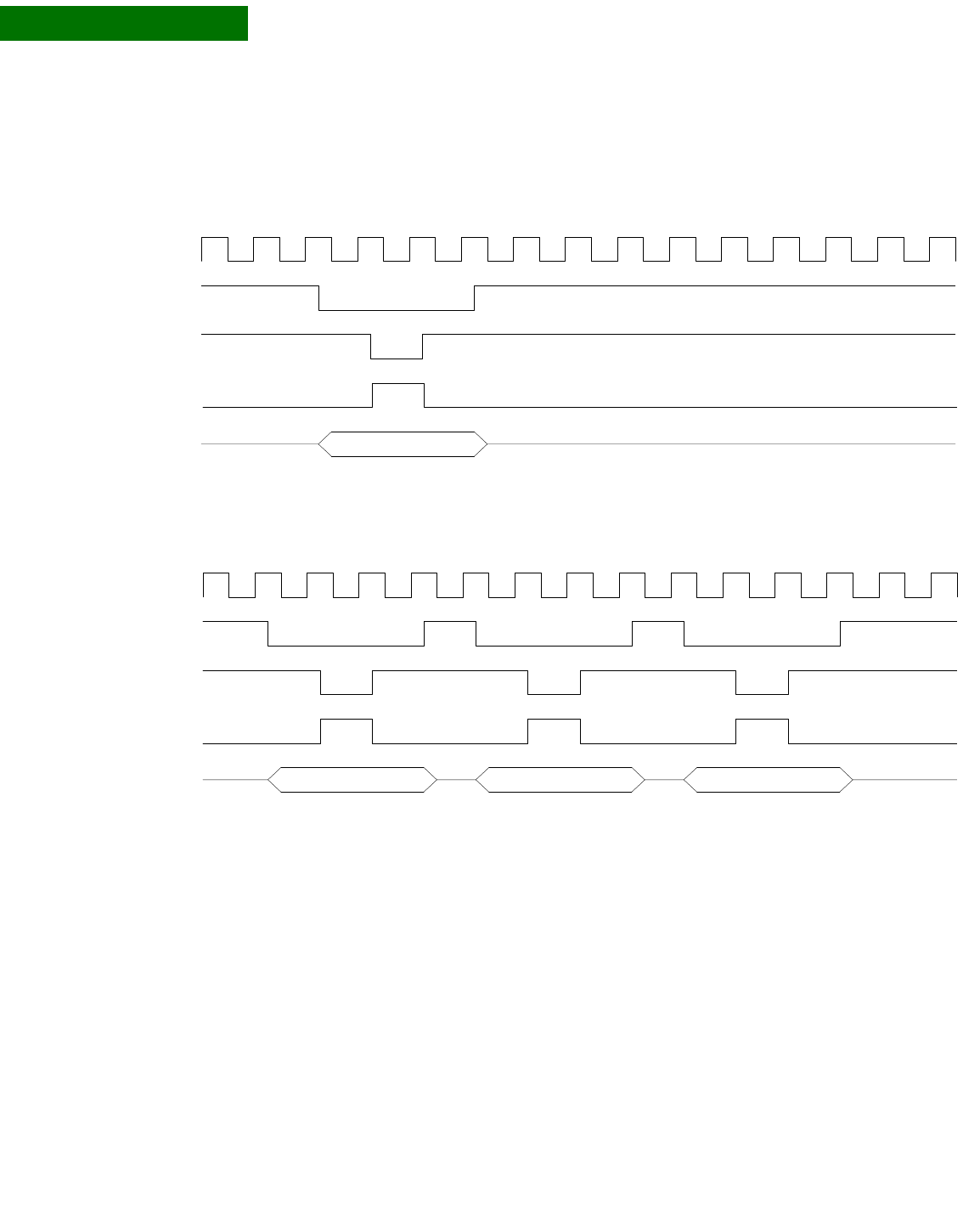

Peripheral DMA

single write access

Peripheral DMA

burst write access

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Peripheral REQ and DONE signaling

The processor treats the REQ and DONE signals as asynchronous, level signals.

REQ signal

The external peripheral can initiate a DMA transfer at any time by asserting the

REQ signal.

The external peripheral can pause the DMA transfer at any time by deasserting

the REQ signal.

The REQ signal can be deasserted during a transfer but if the peripheral is

configured for burst access, the burst completes. The DMA transfer control

logic remains paused until the REQ signal is reasserted.

ADDR &

DATA

st_cs_n[n]

CLK

we_n

Addr/Data Valid

PDEN

CLK

ADDR0/DATA0

st_cs_n[n]

we_n

ADDR &

DATA

ADDR1/DATA1 ADDR2/DATA2

PDEN