SERIAL CONTROL MODULE: SPI

Interrupt Status register

442 Hardware Reference NS9215

Use the Interrupt Enable register to enable interrupt generation on specific events.

Enable the interrupt by writing a 1 to the appropriate bit field(s).

Register

Register bit

assignment

T

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

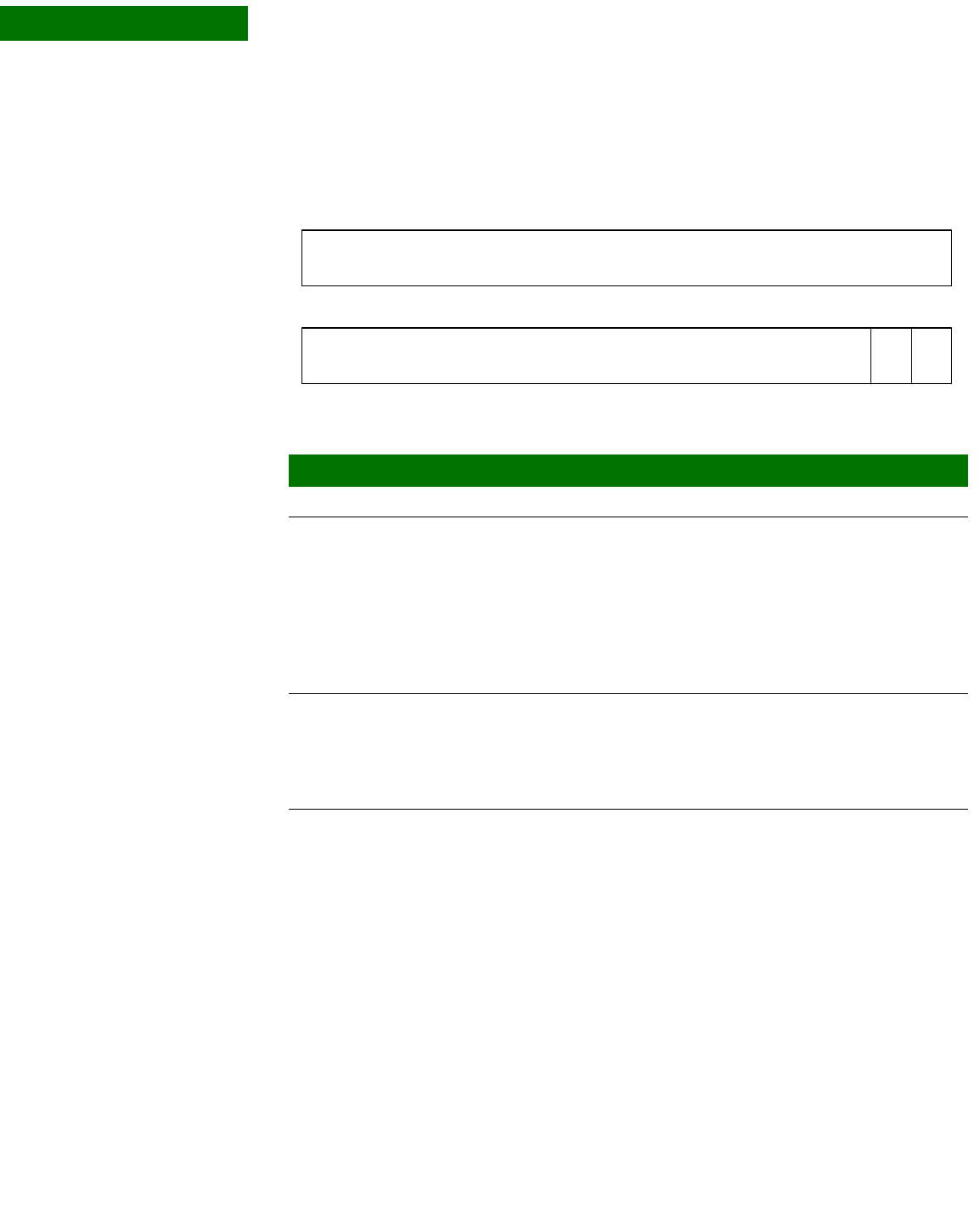

Interrupt Status register

Address: 9003_1024

The Interrupt Status register provides status about SPI events. All events are

indicated by reading a 1 and are cleared by writing a 1.

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Not used

Not used

TX_ IDLE RX_IDLE

Bits Access Mnemonic Reset Description

D31:02 R/W Not used 0 Write this field to 0.

D01 R/W TX_IDLE 0 Enable transmit idle

Enables interrupt generation whenever the transmitter

moves from the active state to the idle state.

In master mode, this indicates that the transmit FIFO

is empty and that the transmitter is not actively

shifting out data.

In slave mode, this indicates that the externally

provided chip select has been deasserted.

D00 R/W RX_IDLE 0 Enable receive idle

Enables interrupt generation whenever the receiver moves

from the active state to the idle state. In either master or

slave mode, this indicates that the chip select signal has

been deasserted.