SYSTEM CONTROL MODULE

Timer 5 Control register

166 Hardware Reference NS9215

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer 5 Control register

Address: A090 01A4

Register

D05:04 R/W Timer mode 0x0 Timer mode

00 Internal timer or external event

01 External low-level gated timer

10 External high-level gated timer

11 Concatenate the lower timer.

Note: When either external gated option is

selected, the time clock select bits deter-

mine the frequency.

D03 R/W Int Sel 0x0 Interrupt select

0 Interrupt disable

1 Generate IRQ

D02 R/W Up Down 0x0 Up/Down select

0 Up counter

1 Down counter

D01 R/W Bit timer 0x0 32 or 16 bit timer

0 16-bit timer

1 32-bit timer

D00 R/W Rel Enbl 0x0 Reload enable

0 Halt at terminal count. The timer must be

disabled, then enabled to reload the timer when

the terminal count is reached.

1 Reload and resume count at terminal count

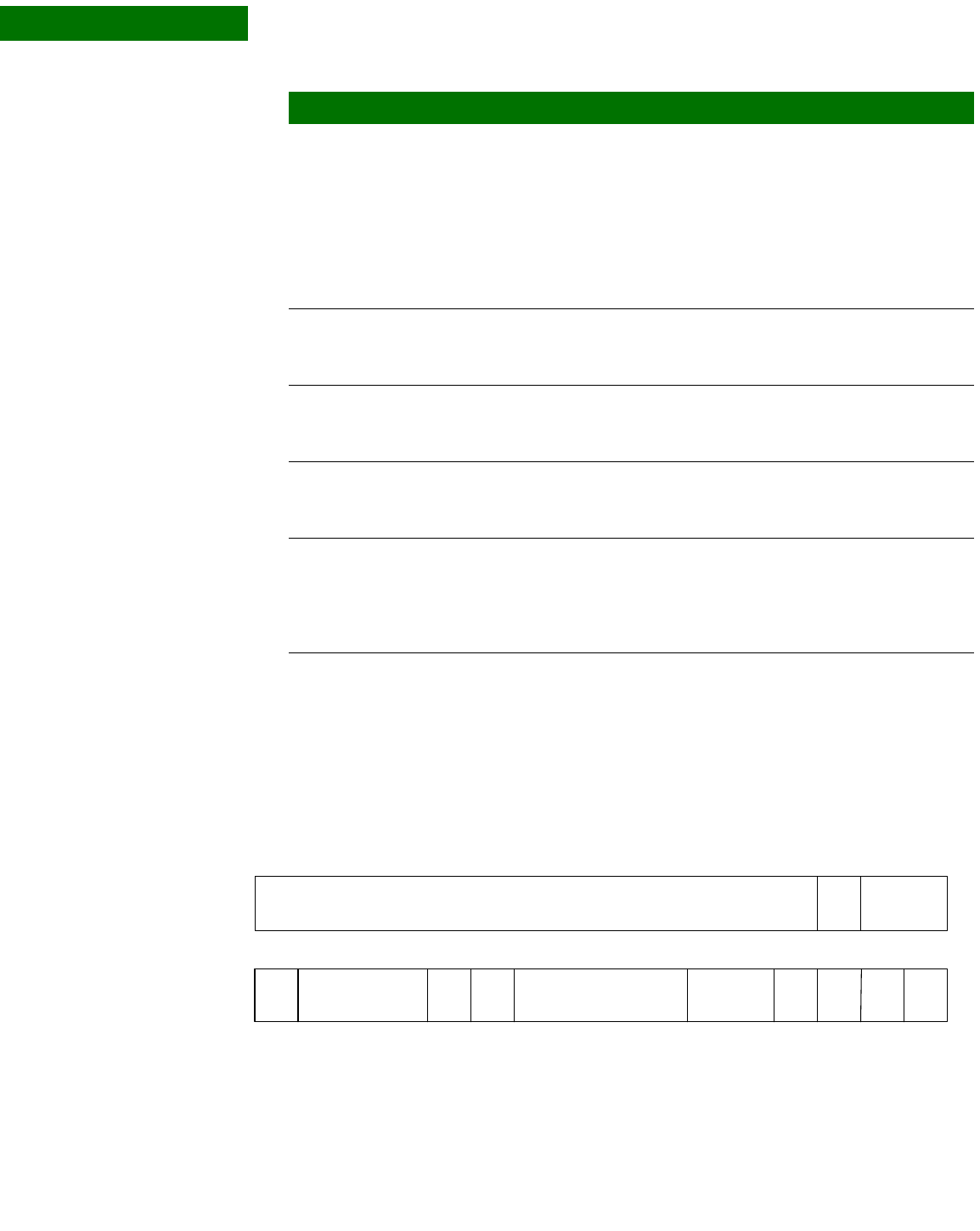

Bits Access Mnemonic Reset Description

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

TCS

Reserved

Cap Comp Debug Int Clr

Timer

Mode

Int Sel

Up

Down

Bit

timer

Rel

Enbl

Rel

Mode

TM2

TE