. . . . .

REAL TIME CLOCK MODULE

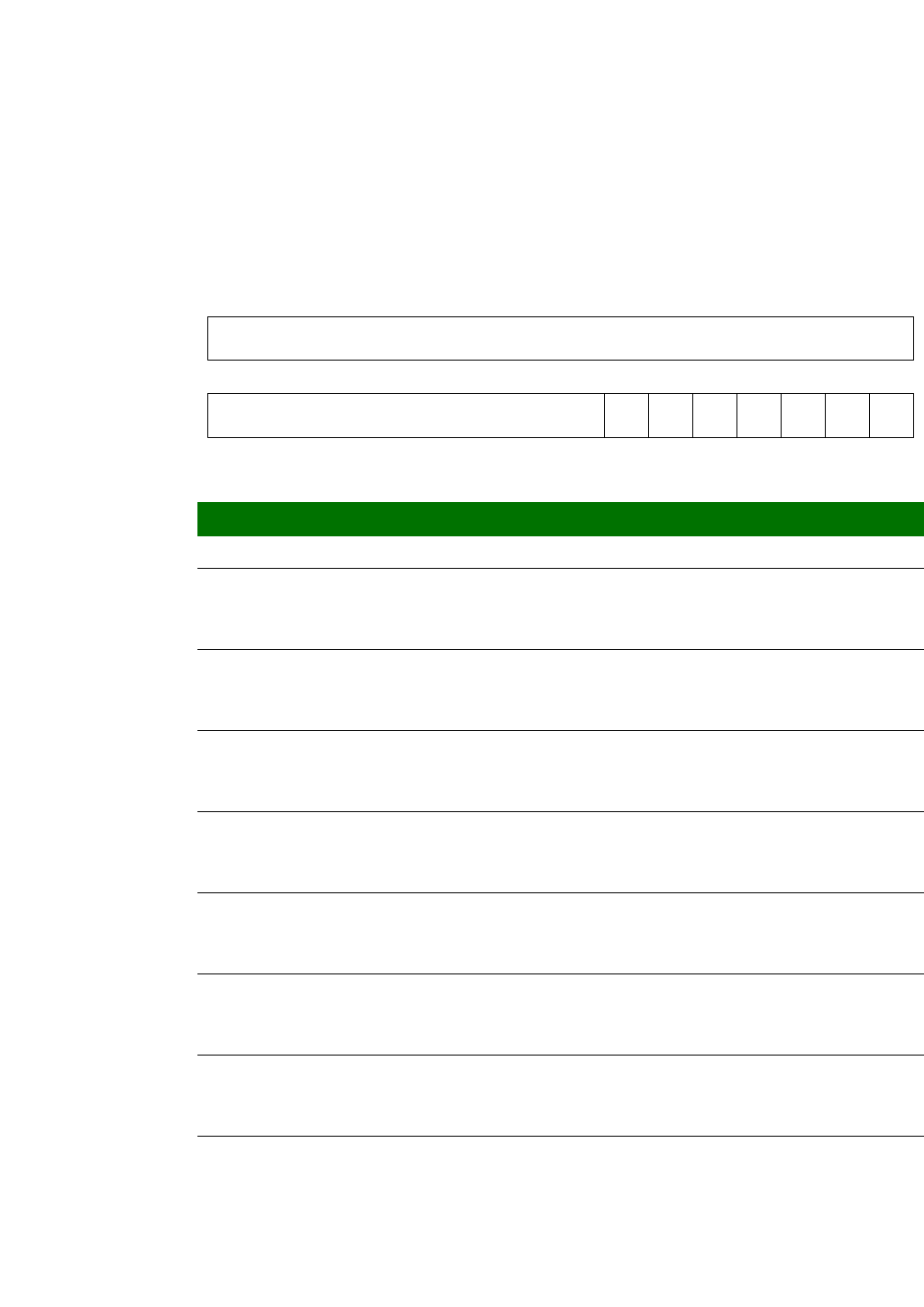

Interrupt Disable register

www.digiembedded.com 469

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Disable register

Address: 9006 0024

The Interrupt Disable register resets interrupts that are currently enables. An

interrupt is disabled by writing a 1, then a 0, to the appropriate disable register bit.

Register

Register bit

assignment

13 12 11 10 9 8 7 6 5 4 3 2 1 015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved

Reserved

Mnth

Dis

Date

Dis

Hour

Dis

Min

Dis

Sec

Dis

Hsec

Dis

Alrm

Dis

Bits Access Mnemonic Reset Description

D31:07 N/A Reserved N/A N/A

D06 W Alrm Dis 0x0 Alarm interrupt disable

0 Enable alarm interrupt

1 Disable alarm interrupt

D05 W Mnth Dis 0x0 Month interrupt disable

0 Enable month interrupt

1 Disable month interrupt

D04 W Date Dis 0x0 Date interrupt disable

0 Enable date interrupt

1 Disable date interrupt

D03 W Hour Dis 0x0 Hour interrupt disable

0 Enable hour interrupt

1 Disable hour interrupt

D02 W Min Dis 0x0 Minute interrupt disable

0 Enable minute interrupt

1 Disable minute interrupt

D01 W Sec Dis 0x0 Second interrupt disable

0 Enable second interrupt

1 Disable second interrupt

D00 W Hsec Dis 0x0 Hundredth of a second interrupt disable

0 Enable hundredth second interrupt

1 Disable hundredth second interrupt