SERIAL CONTROL MODULE: HDLC

HDLC Clock Divider Low

430 Hardware Reference NS9215

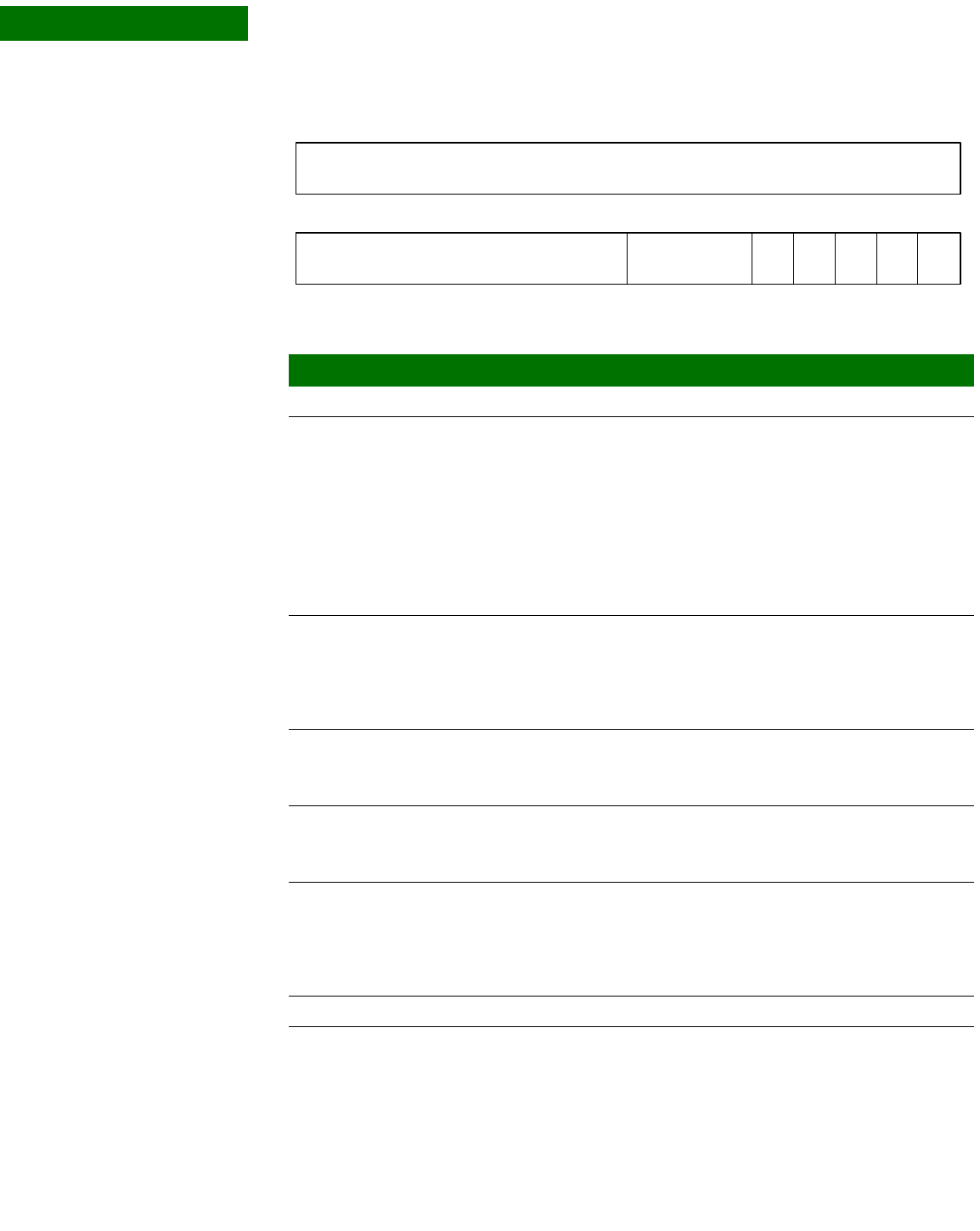

Register

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

HDLC Clock Divider Low

Address: 9002_9118

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved

I

MODE

Reserved

H

MODE

ECLK Not used

CMODE

U

MODE

Bits Access Mnemonic Reset Description

D31:08 R Not used 0 Write this field to 0.

D07:05 R/W CMODE 0 Coding mode

000 NRZ data encoding for receiver and transmitter

010 RZI data encoding for receiver and transmitter

100 Biphase-Level (Manchester) data encoding for

receiver and transmitter

110 Biphase-Space data encoding for receiver and

transmitter

111 Biphase-Mark data encoding for receiver and

transmitter

D04 R/W HMODE 0 HDLC mode

0 Normal HDLC data encoding

1 Enable NRZI coding (1/4 bit-cell IRDA-compliant).

This mode can be used only with internal clock and

NRZ data encoding.

D03 R/W IMODE 0 Transmit idle mode

0 Transmit flags while in idle mode

1 Transmit all 1s while in idle mode

D02 R/W UMODE 0 Underrun mode

0 Transmit flag on underrun

1 Transmit abort on underrun

D01 R/W ECLK 0 External clock mode

0 The HDLC module will use separate external receive

and transmit clocks

1 The HDLC receiver and transmitter will both use the

external transmit clock.

D00 R Not used 0 Always write 0 to this bit.