. . . . .

SERIAL CONTROL MODULE: UART

Interrupt Enable register

www.digiembedded.com 393

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Enable register

Address: 9001_1004 / 9001_9004 / 9002_1004 / 9002_9004

Use the Interrupt Enable register to enable interrupt generation on specific events.

Enable the interrupt by writing a 1 to the appropriate bit field(s).

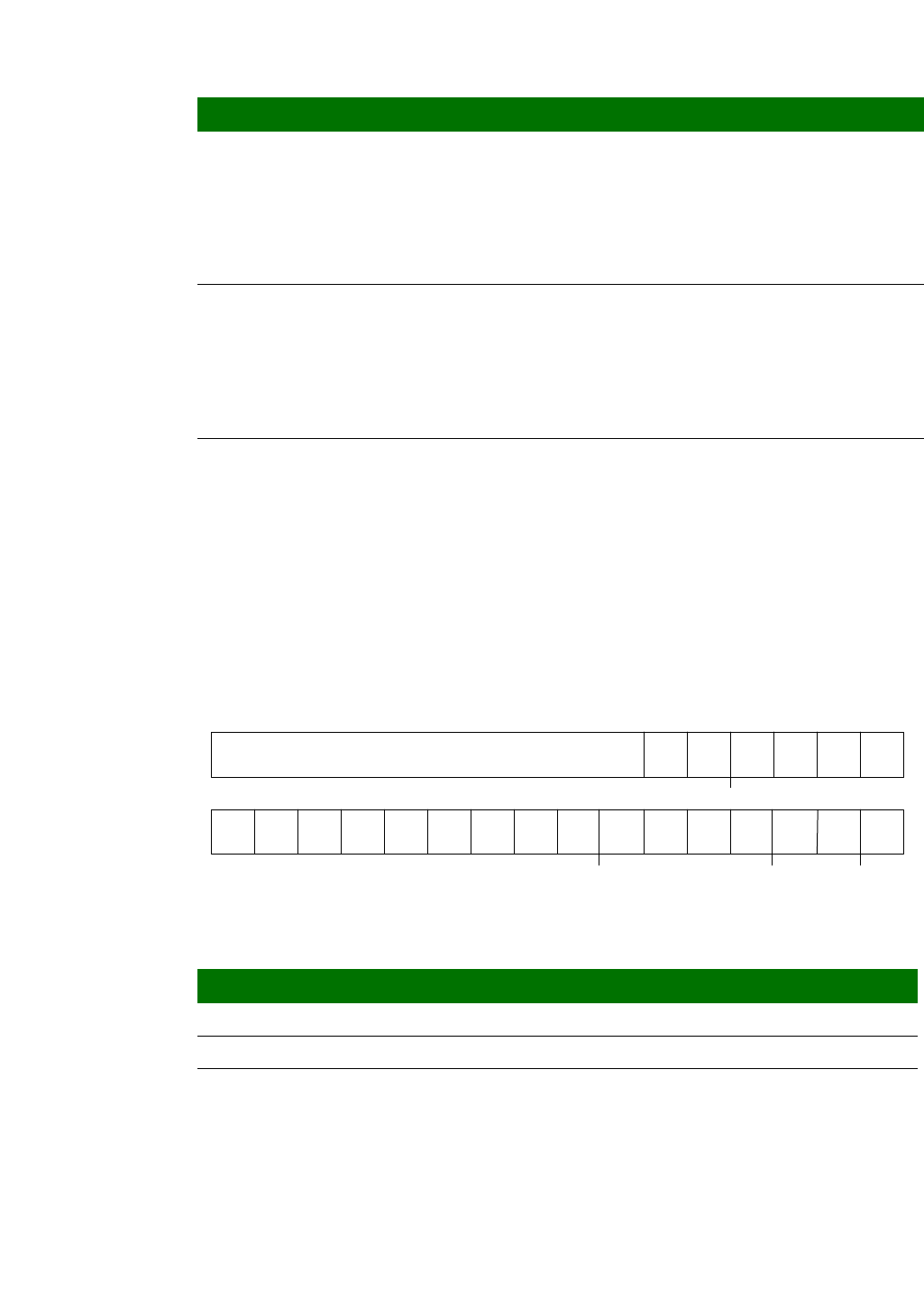

Register

Register bit

assignment

D03:02 R/W RS485OFF 00 RS485 transceiver deassertion control

In bit times after the stop bit period

00 0

01 1

10 1.5

11 2

D01:00 R/W RS485ON 00 RS485 transceiver assertion control

In bit times before the falling edge of the start bit

00 0

01 1

10 1.5

11 2

Bits Access Mnemonic Reset Description

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

MATCH

0

CGAPBGAP

CTS TBC

TX_

IDLE

PARITY

FRA

ME

Not used

BREA

K

MATCH

4

RI

Reser

ved

FORCE OFLOW

RXCLS

MATCH

3

MATCH

2

MATCH

1

DSR DCD RBC

RX_

IDLE

Bits Access Mnemonic Reset Description

D31:22 R/W Not used 0 Write this field to 0.

D21 R/W Reserved 0 Always write to 0.

D20 R/W FORCE 0 Enable force complete

Enables interrupt generation when a force character

transmission operation has completed.