I/O HUB MODULE

Control and status register address maps

370 Hardware Reference NS9215 31 March 2008

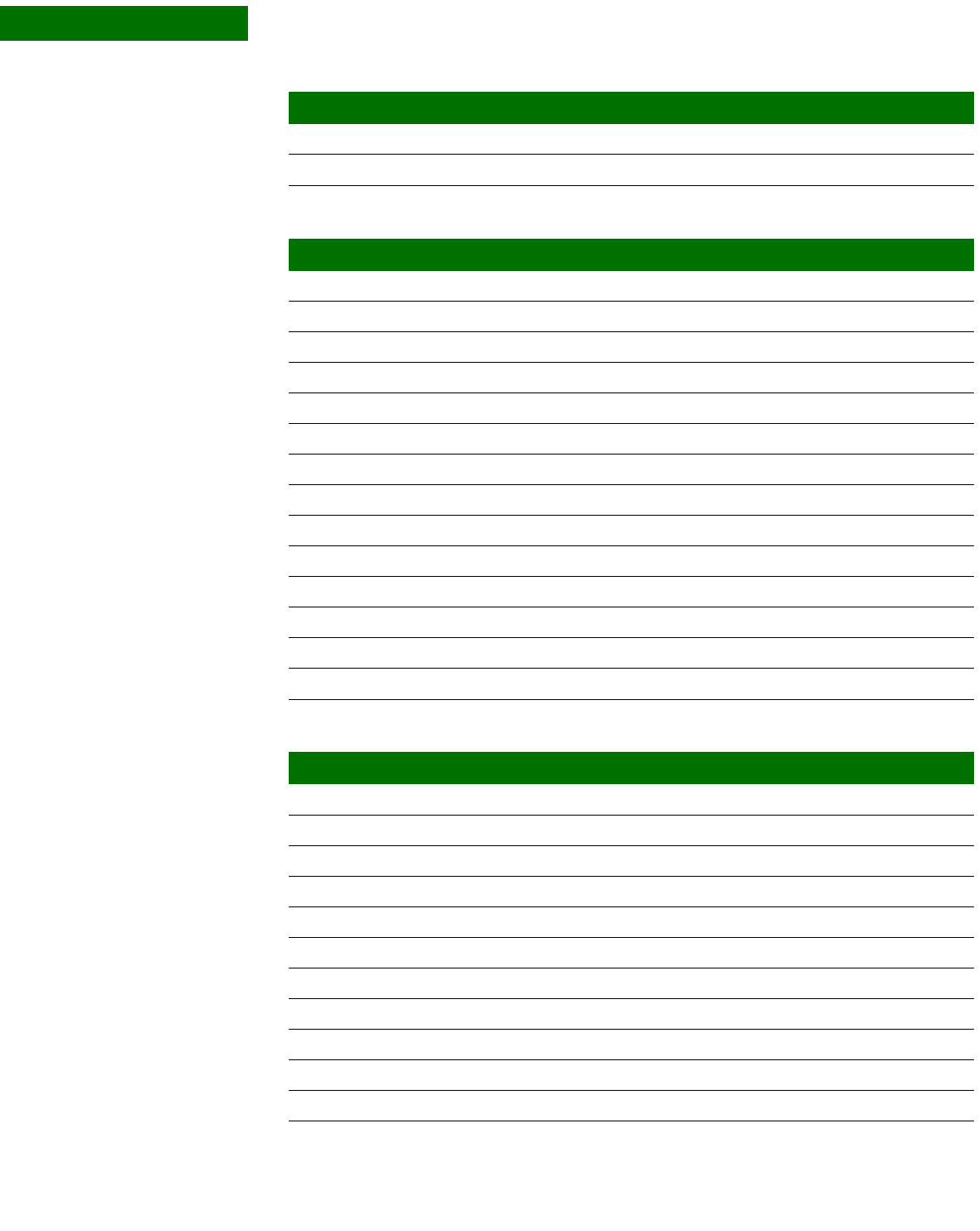

UART C register

address map

UART D register

address map

0x9001_8030 – 0x9001_8FFF Reserved

0x9001_9000 – 0x9001_9FFF UART B CSR Space

Register Offset Description (31:00)

Register Offset Description (31:00)

0x9002_0000 UART C Interrupt and FIFO Status

0x9002_0004 UART C DMA RX Control

0x9002_0008 UART C DMA RX Buffer Descriptor Pointer

0x9002_000C UART C DMA RX Interrupt Configuration register

0x9002_0010 UART C Direct Mode RX Status FIFO

0x9002_0014 UART C Direct Mode RX Data FIFO

0x9002_0018 UART C DMA TX Control

0x9002_001C UART C DMA TX Buffer Descriptor Pointer

0x9002_0020 UART C DMA TX Interrupt Configuration register

0x9002_0024 Reserved

0x9002_0028 UART C Direct Mode TX Data FIFO

0x9002_002C UAT C Direct Mode TX Data Last FIFO

0x9002_0030 – 0x9002_0FFF Reserved

0x9002_1000 – 0x9002_7FFF UART C CSR Space

Register Offset Description (31:00)

0x9002_8000 UART D Interrupt and FIFO Status

0x9002_8004 UART D DMA RX Control

0x9002_8008 UART D DMA RX Buffer Descriptor Pointer

0x9002_800C UART D DMA RX Interrupt Configuration register

0x9002_8010 UART D DIrect Mode RX Status FIFO

0x9002_8014 UART D Direct Mode RX Data FIFO

0x9002_8018 UART D DMA TX Control

0x9002_801C UART D DMA TX Buffer Descriptor Pointer

0x9002_8020 UART D DMA TX Interrupt Configuration register

0x9002_8024 Reserved

0x9002_8028 UART D Direct Mode TX Data FIFO

0x9002_802C UART D Direct Mode TX Data Last FIFO