SERIAL CONTROL MODULE: UART

Hardware-based flow control

388 Hardware Reference NS9215

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Hardware-based flow control

The UART module provides expanded functionality for hardware-based flow control.

The RTS signal normally indicates the state of the receive FIFO. The CTS signal

normally halts the transmitter. With this UART module, the RI, CTS, DCD, or DSR

signals can halt the transmitter. Program these features using the HWFLOW bits in

the Wrapper Configuration register.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Character-based flow control (XON/XOFF)

Traditional character-based flow control requires the processor to match the flow

control characters and control the transmitter accordingly. This UART module

performs the character matching function in hardware and automatically updates

the state of the transmitter, which allows character-based flow control to achieve

the same response time as hardware-based flow control.

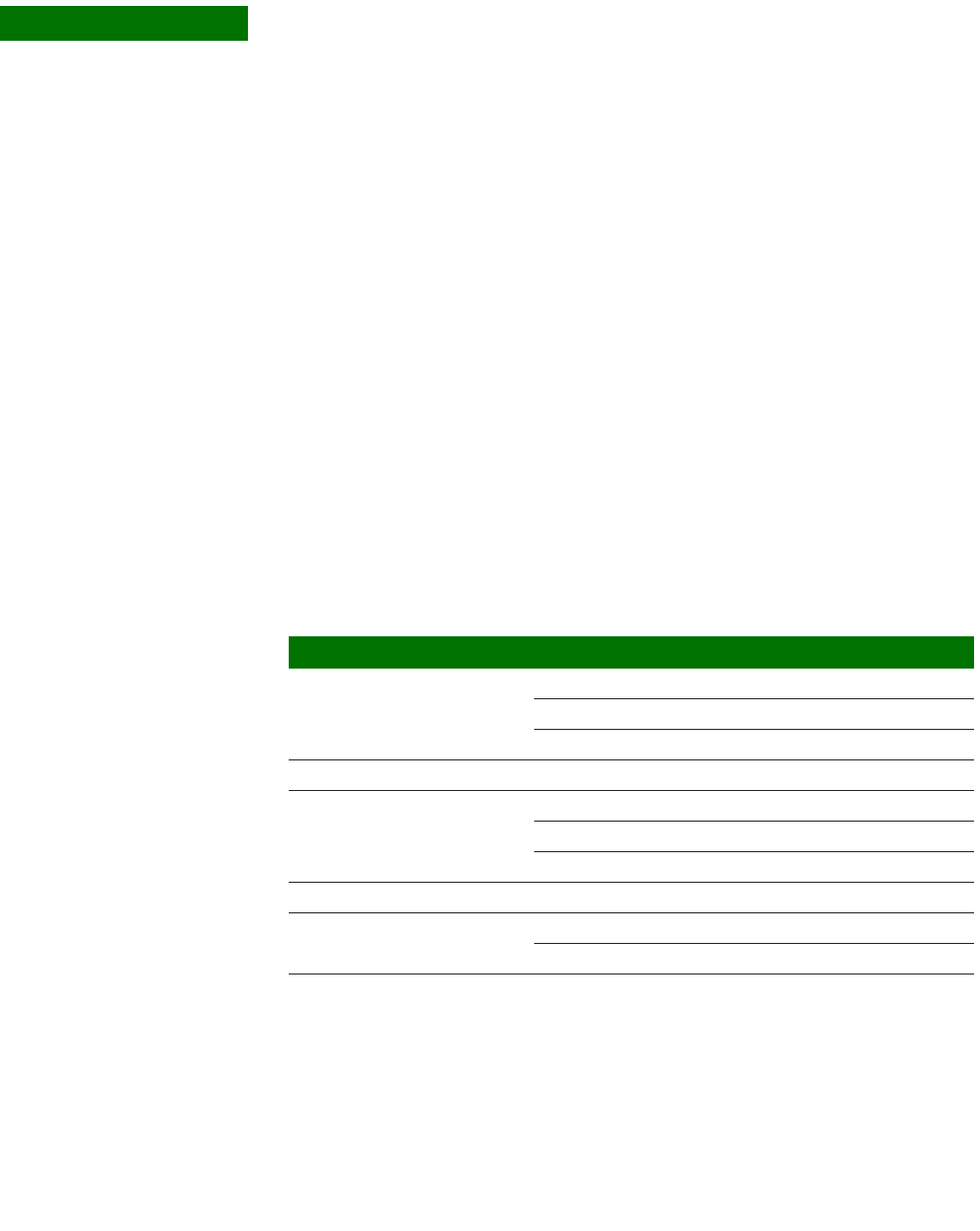

Example

configuration

Configure the character-based flow control using at least two Receive Character

Match registers and the Receive Character-Based Flow Control register. This table

shows a sample configuration for a system transferring 8 data bits per character.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Forced character transmission

UART provides a mechanism in which you can bypass data in the transmit FIFO with

a specific character. The specified character is transmitted after the current

Control register Field Value Comment

Receive Character Match Control

Register 0

ENABLE 1 Enable character match

MASK 0x00 Mask bits

DATA 0x7e Define character

Receive Character Match Control

Register 1

ENABLE 1 Enable character match

MASK 0x00 Mask bits

DATA 0x81 Define character

Receive Character-Based Flow

Control register

FLOW0 0x2 XON when matched

FLOW1 0x3 XOFF when matched