SERIAL CONTROL MODULE: SPI

SPI controller

434 Hardware Reference NS9215

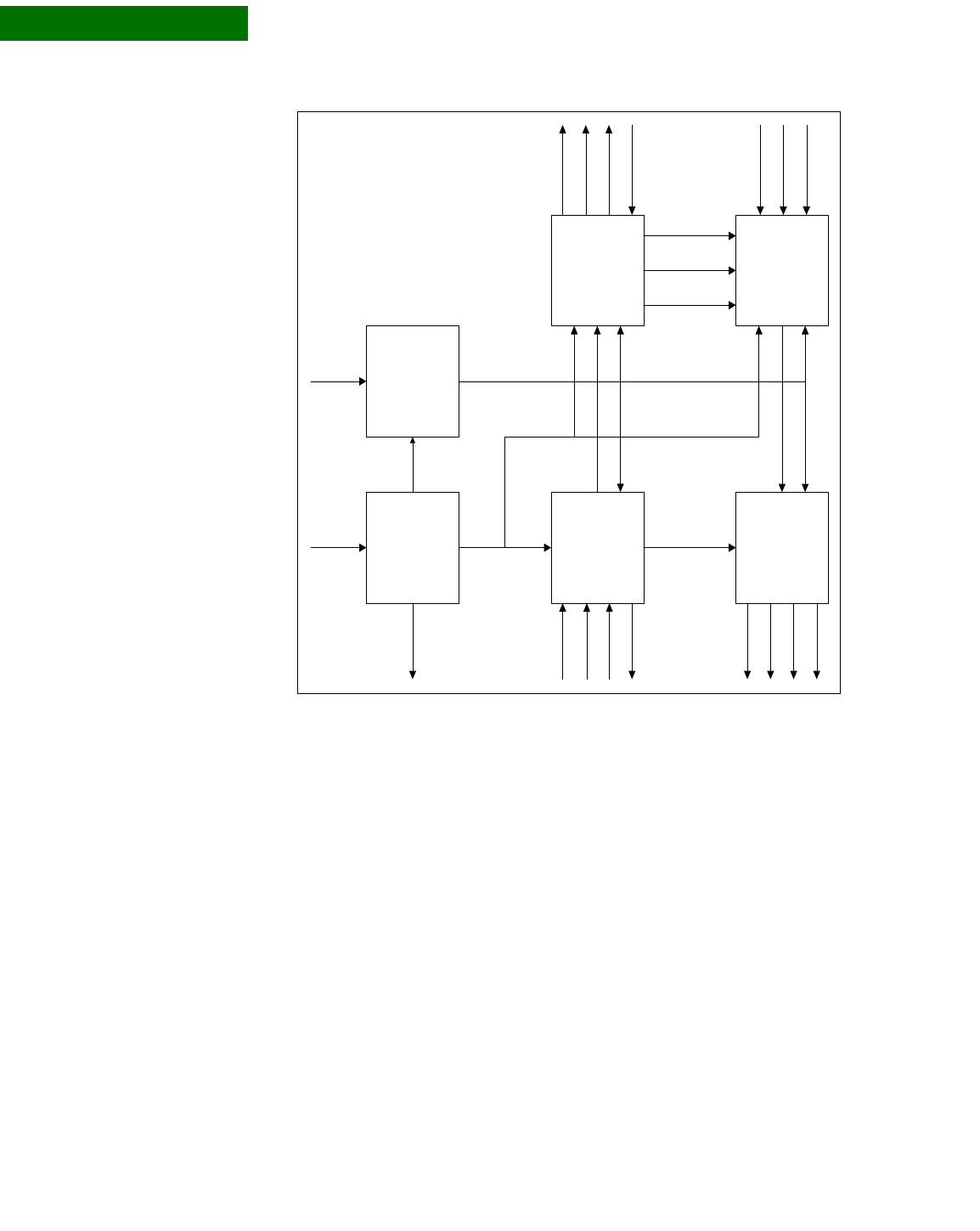

SPI module

structure

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SPI controller

The SPI controller provides a full-duplex, synchronous, character-oriented data

channel between master and slave devices, using a four-wire interface (RXD, TXD,

CLK, CS#). The master interface operates in a broadcast mode. The slave interface

is activated using the CS# signal. You can configure the master interface to address

various slave interfaces using the GPIO pins.

Simple

parallel/serial

data conversion

SPI provides simple parallel/serial data conversion to stream serial data between

memory and a peripheral. The SPI port has no protocol associated with it other than

transferring information in multiples of 8 bits.

Full duplex

operation

The SPI port can operate in full-duplex mode. Information transfer is controlled by a

single clock signal. The clock and chip select signals are chip outputs for a master

mode operation and inputs for a slave mode operation.

Config

AHB Bus

valid

be[1:0]

data[31:0]

read

write

be[1:0]

data[31:0]

status[6:0]

sys_pll_out

spi_clk

spi_clk_out

spi_tx_d

spi_cs_out_n

spi_cs_in_n

spi_cs_in_n

spi_rx_d

spi_clk_in

spi_tx_d

spi_clk_out

spi_cs_out_n

spi_irq

Transmit

State

Machi ne

Receive

State

Machi ne

Clock

Generation

Transmit

Fifo

Interface

Receive

Fifo

Interface