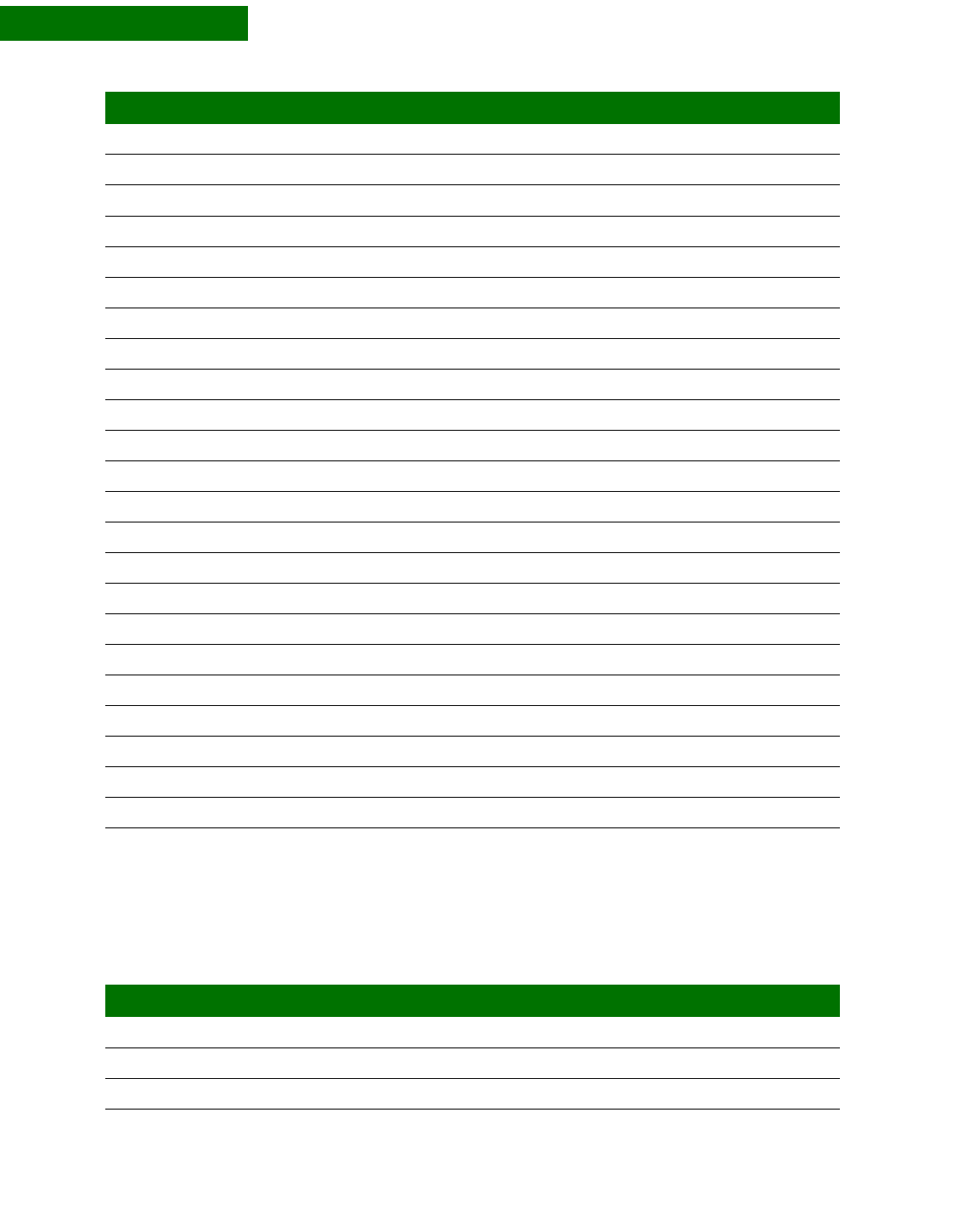

PINOUT (265)

Ethernet interface MAC

30 Hardware Reference NS9215

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ethernet interface MAC

A10 data_mask[3] O 4 byte_enable data[31:24}

B11 data_mask[2] O 4 Byte enable data[23:16]

B10 data_mask[1] O 4 Byte enable data[15:08]

A11 data_mask[0] O 4 Byte enable data {07:00]

A9 ns_ta_strb I Slow peripheral transfer acknowledge

A6 rw_n O 4 Transfer direction

B7 clk_en[3] O 4 SDRAM clock enable

D7 clk_en[2] O 4 SDRAM clock enable

A7 clk_en[1] O 4 SDRAM clock enable

B8 clk_en[0] O 4 SDRAM clock enable

B4 cs[7] O 4 Chip select 7, dy_cs3

A3 cs[6] O 4 Chip select 6, st_cs3

A4 cs[5] O 4 Chip select 5, dy_cs2

C5 cs[4] O 4 Chip select 4, st_cs2

B5 cs[3] O 4 Chip select 3, dy_cs1

B6 cs[2] O 4 Chip select 2, st_cs1 (Flash boot)

D6 cs[1] O 4 Chip select 1, dy_cs0 (Boot sdram)

C6 cs[0] O 4 Chip select 0, st_cs0

C4 ras_n O 4 SDRAM RAS

A2 cas_n O 4 SDRAM CAS

C7 we_n O 4 SDRAM write enable

B3 ap10 O 4 SDRAM A10(AP)

A8 st_oe_n O 4 Static output enable

a. addr [27:24] reset to gpio mode. These address lines cannot be used for boot.

b. gpio[31:16] reset to memory data bus data [15:0].

Pin Signal U/D I/O OD Description

Pin Signal U/D I/O OD Description

A12 mdc / gpio[32] U I/O 2 MII clock

D11 mdio / gpio[35] U I/O 2 MII data

B12 tx_clk / gpio[33] U I/O 2 TX clock

A16 txd[3] / gpio[47] U I/O 2 TX data 3