ETHERNET COMMUNICATION MODULE

Ethernet General Control Register #2

282 Hardware Reference NS9215

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

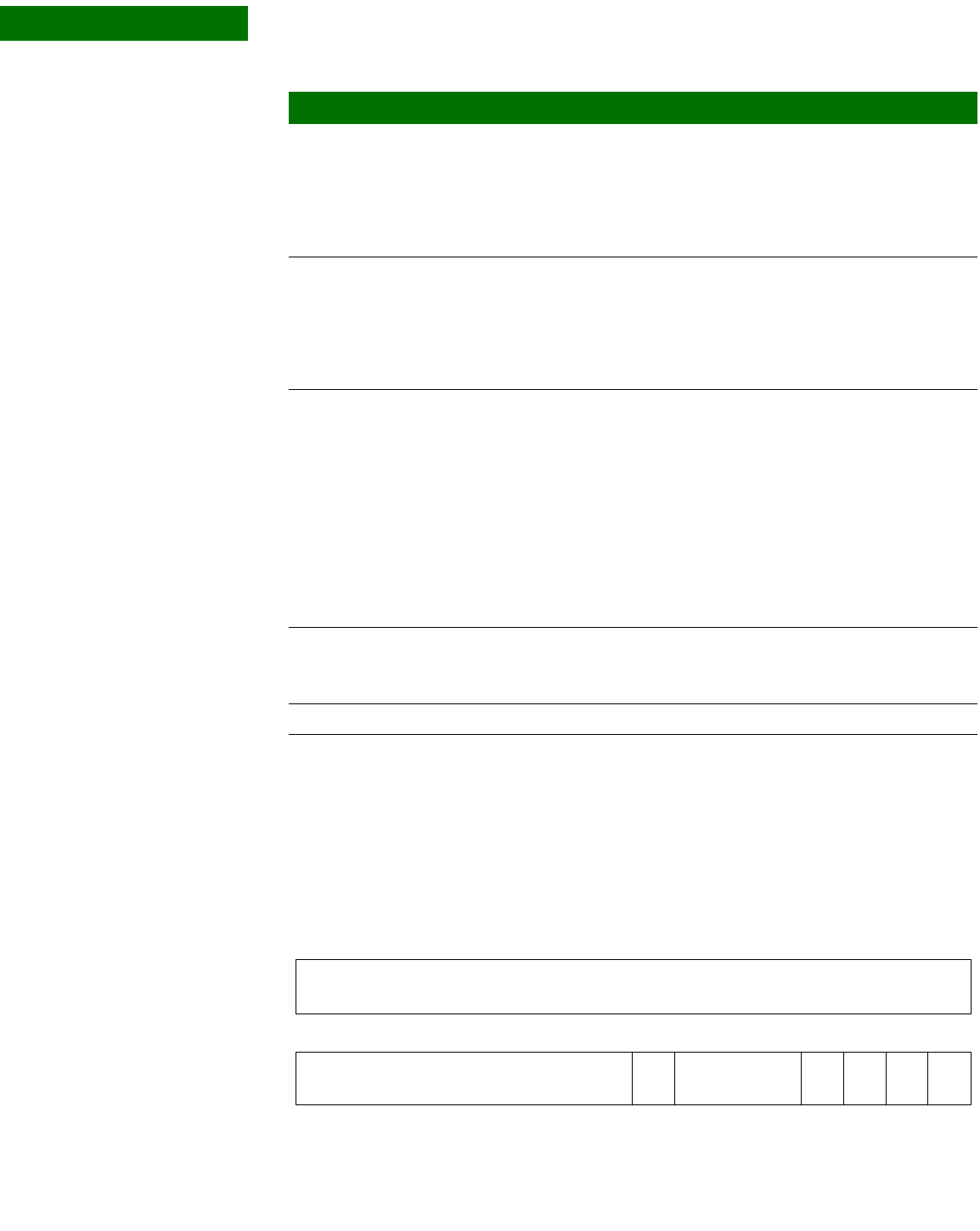

Ethernet General Control Register #2

Address: A060 0004

Register

D10 R/W RXALIGN 0 Align RX data

0 Standard receive format. The data block immediately

follows the 14-byte header block.

1 The receiver inserts a 2-byte padding between the 14-

byte header and the data block, causing longword

alignment for both the header and data blocks.

D09 R/W MAC_HRST 1 MAC host interface soft reset

0 Restore MAC, STAT, SAL, RX_WR, and TX_RD to

normal operation.

1 Reset MAC, STAT, programmable registers in SAL,

RX_WR, and TX_RD. Keep high for minimum of

5μsec to guarantee that all functions get reset.

D08 R/W ITXA 0 Insert transmit source address

0 Source address for Ethernet transmit frame taken from

data in TX_FIFO.

1 Insert the MAC Ethernet source address into the

Ethernet transmit frame source address field.

Set to force the MAC to automatically insert the Ethernet

MAC source address into the Ethernet transmit frame

source address. The SA1, SA2, and SA3 registers provide

the address information. When the ITXA bit is cleared, the

Ethernet MAC source address is taken from the data in the

TX_FIFO.

D07 R/W RXRAM 1 RX FIFO RAM access

0 CPU access to the RX FIFO RAM is disabled

1 CPU access to the RX FIFO RAM is enabled

D06:00 N/A Reserved N/A N/A

Bits Access Mnemonic Reset Description

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Not used

Not used TCLER Not used TKICK

CLRCNT

STENAUTOZ