SYSTEM CONTROL MODULE

Clock Configuration register

180 Hardware Reference NS9215

Register

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

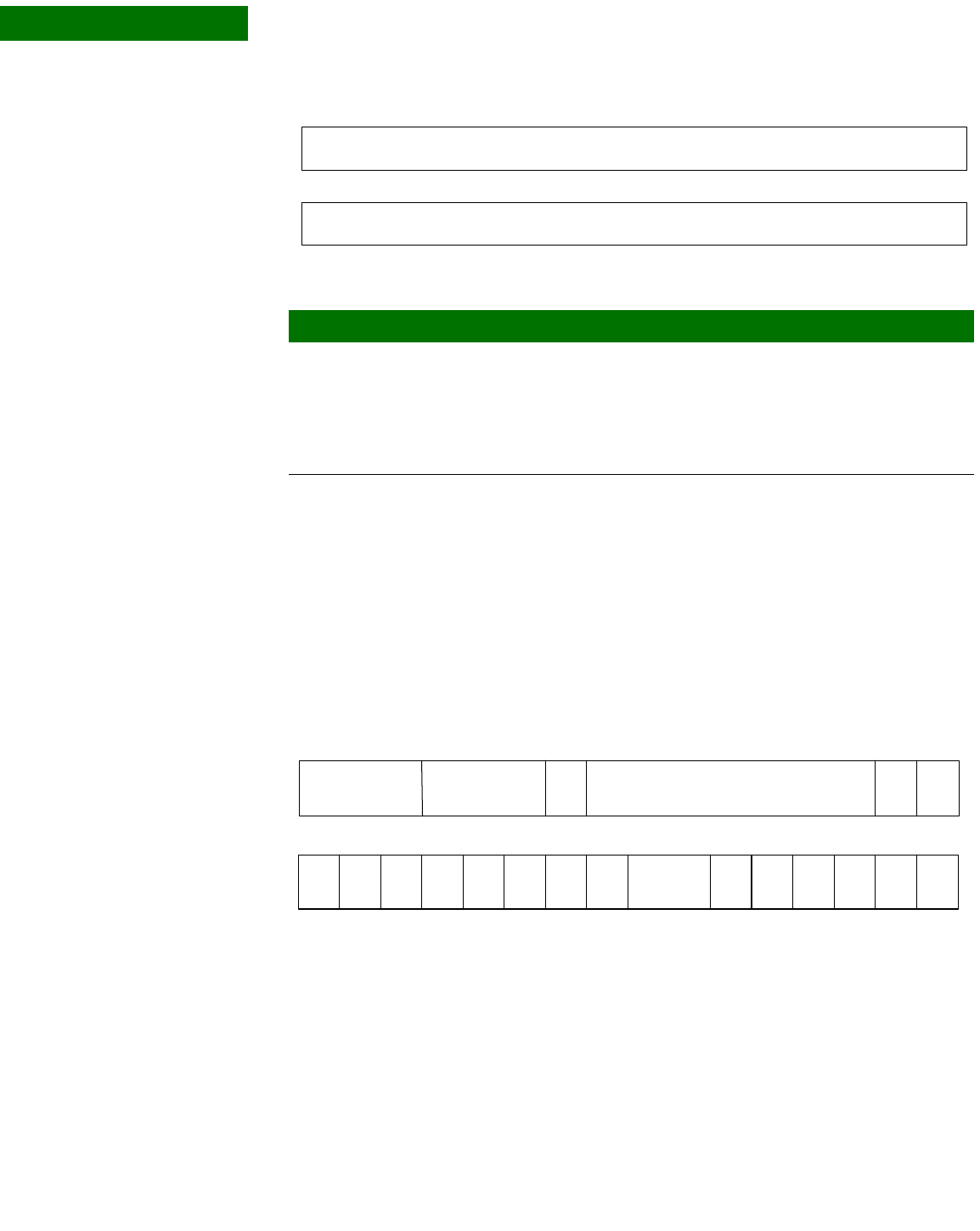

Clock Configuration register

Address: A090 017C

The Clock Configuration register enables and disables clocks to each module on the

AHB bus.

Register

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Watchdog Timer

Watchdog Timer

Bits Access Mnemonic Reset Description

D31:00 R/W Watchdog timer 0x0 Watchdog timer

A read to this register gives the current value of

the watchdog timer, but will not change the

contents.

A write to the register changes the contents

based on the write data value.

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

CCSel

ADC

CSC Max CSC Reserved

MCOu t

1

Reser

ved

RTC

EXT

DMA

IO

hub

I

2

C

Reser

ved

AES Reserved SPI

UART

D

UART

C

UART

A

MCOu t

0

Eth

MAC

UART

B