SERIAL CONTROL MODULE: HDLC

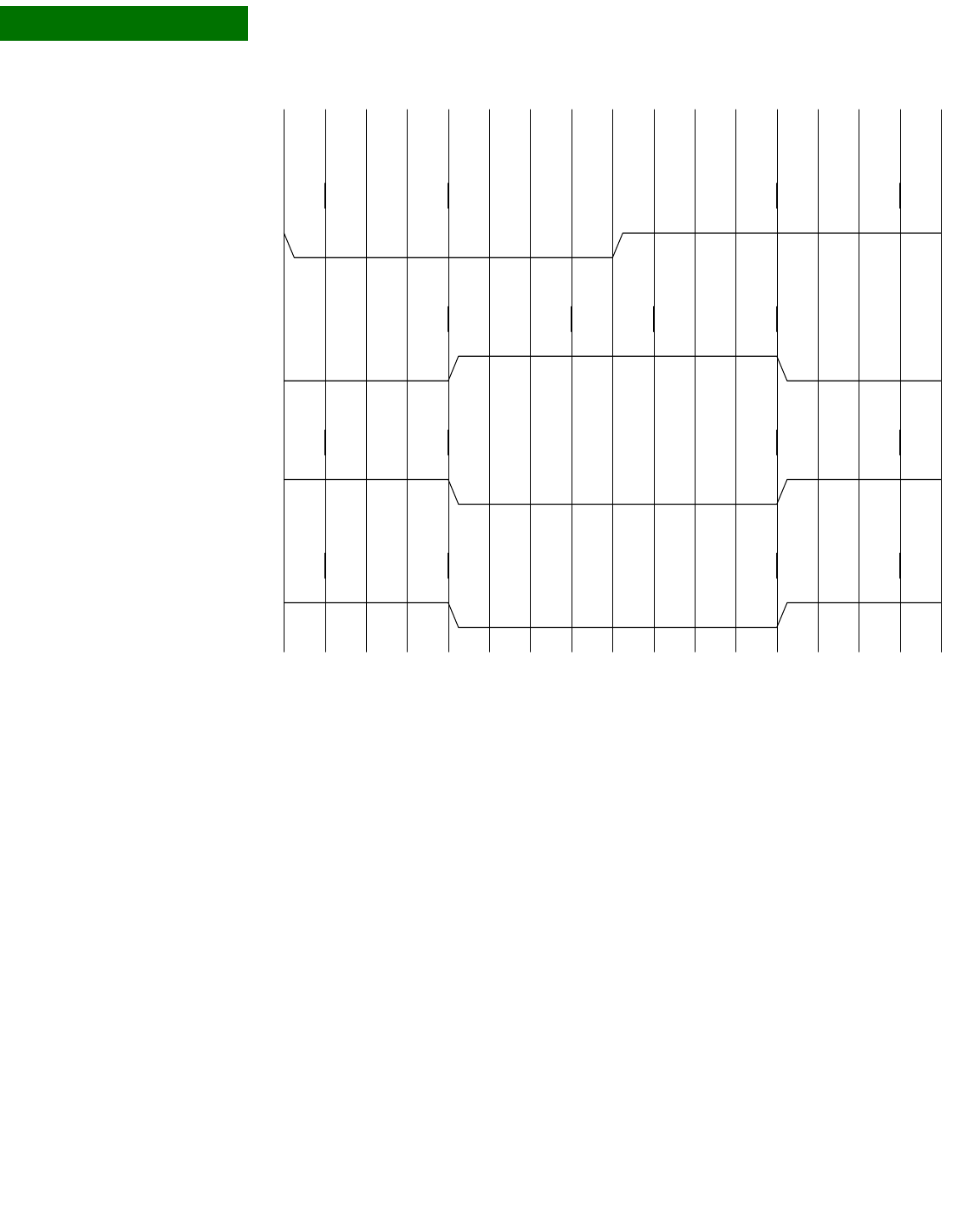

DPLL operation: Adjustment ranges and output clocks

420 Hardware Reference NS9215

NRZ and NRZI

encoding

With NRZ and NRZI encoding, all transitions occur on bit-cell boundaries and the data

should be sampled in the middle of the bit cell.

If a transition occurs after the expected bit-cell boundary, but before the

midpoint, the DPLL needs to lengthen the count to line up the bit-cell

boundaries; this corresponds to the “add one” and “add two” regions of the

figure.

If a transition occurs before the bit-cell boundary, but after the midpoint, the

DPLL needs to shorten the count to line up the bit-cell boundaries; this

corresponds to the “subtract one” and “subtract two” regions shown in the

figure.

The DPLL makes no adjustment if the bit-cell boundaries are lined up within

one count of the divide-by-sixteen counter. The regions that adjust the count

by two allow the DPLL to synchronize faster to the data stream when starting

up.

Biphase-Level

encoding

With biphase-level encoding, there is a guaranteed “clock” transition at the center of

every bit-cell and optional “data” transitions at the bit-cell boundaries. The DPLL

NRZI adj

NRZI Clock

Bi-L adj

Bi-L Clock

Bi-S adj

Bi-S Clock

Bi-M adj

Bi-M Clock

Bit cell

add one add two subtract two subtract one nonenone

ignore transitions subtract one none add one ignore transitions

ignore transitionsnone add one subtract one none

ignore transitionsnone add one subtract one none