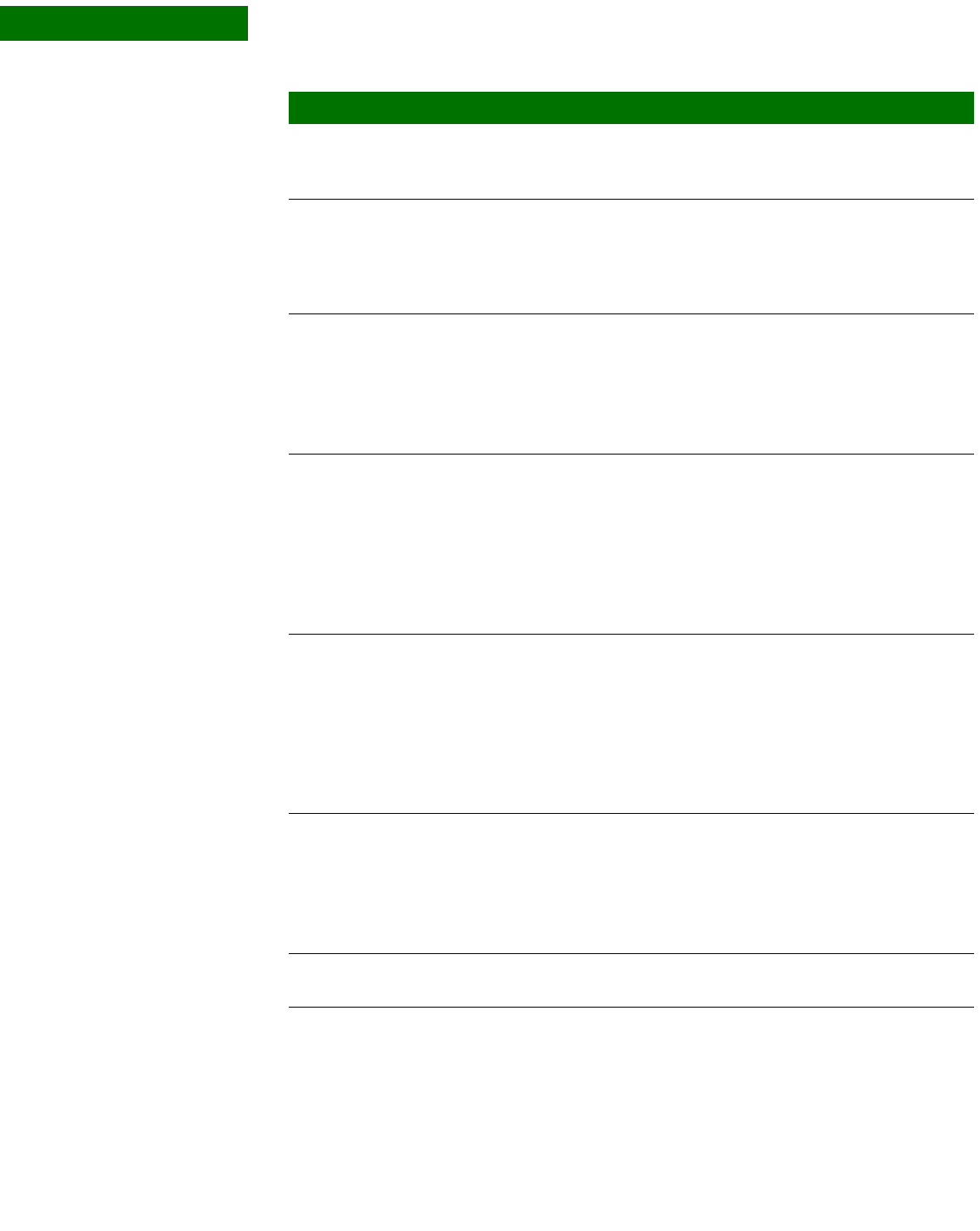

I/O HUB MODULE

[Module] Interrupt and FIFO Status register

374 Hardware Reference NS9215 31 March 2008

D26 R/W* RXFOFIP 0x0 RX FIFO overflow interrupt pending

Set when the RX FIFO finds an overflow

condition.

D25 R/W* RXFSRIP 0x0 RX FIFO service request interrupt pending

(RX)

Set when the RX FIFO level rises above the

receive FIFO threshold (in the RX Interrupt

Configuration register).

D24 R/W* TXNCIP 0x0 Normal completion interrupt pending (TX)

Set when a buffer is closed under normal

conditions. An interrupt is generated when the I bit

is set in the current buffer descriptor.

A normal DMA completion occurs when the

buffer length field expires.

D23 R/W* TXECIP 0x0 Error completion interrupt pending (TX)

Set when the DMA channel finds either a bad

buffer descriptor or a bad data buffer pointer.

The DMA channel remains in the ERROR state

until the CE bit in the DMA Control register is

cleared and then set again. The DMA channel then

uses the buffer descriptor as set in the index

control field.

D22 R/W* TXNRIP 0x0 Buffer not ready interrupt pending (TX)

Set when the DMA channel finds a buffer

descriptor with the F bit not set.

The DMA channel remains in the ERROR state

until the CE bit in the DMA Control register is

cleared and then set again. The DMA channel then

uses the buffer descriptor as set in the index

control field.

D21 R/W* TXCAIP 0x0 Channel abort interrupt pending (TX)

Set when the DMA channel finds the channel

abort (CA) control bit set.

The DMA controller closes the current buffer

descriptor and remains in the IDLE state until the

CA bit is cleared and the CE bit is set.

D20 R/W* TXFUFIP 0x0 TX FIFO underflow interrupt pending

Set when the TX FIFO finds an underflow.

D19 R/W* TXFSRIP 0x0 TX FIFO service request interrupt pending

(TX)

Set when the TX FIFO level drops below the

transmit FIFO threshold (in the TX Interrupt

Configuration register).

Bit(s) Access Mnemonic Reset Description