I2C MASTER/SLAVE INTERFACE

I2C registers

450 Hardware Reference NS9215

bus owner, the transaction goes through. If the module loses bus arbitration, an

M_ARBIT_LOST interrupt is generated to the host processor and the command must

be reissued.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I

2

C registers

All registers have 8-bit definitions, but must be accessed in pairs. For example,

TX_DATA_REG and CMD_REG are written simultaneously and RX_DATA_REG and

STATUS_REG are read simultaneously.

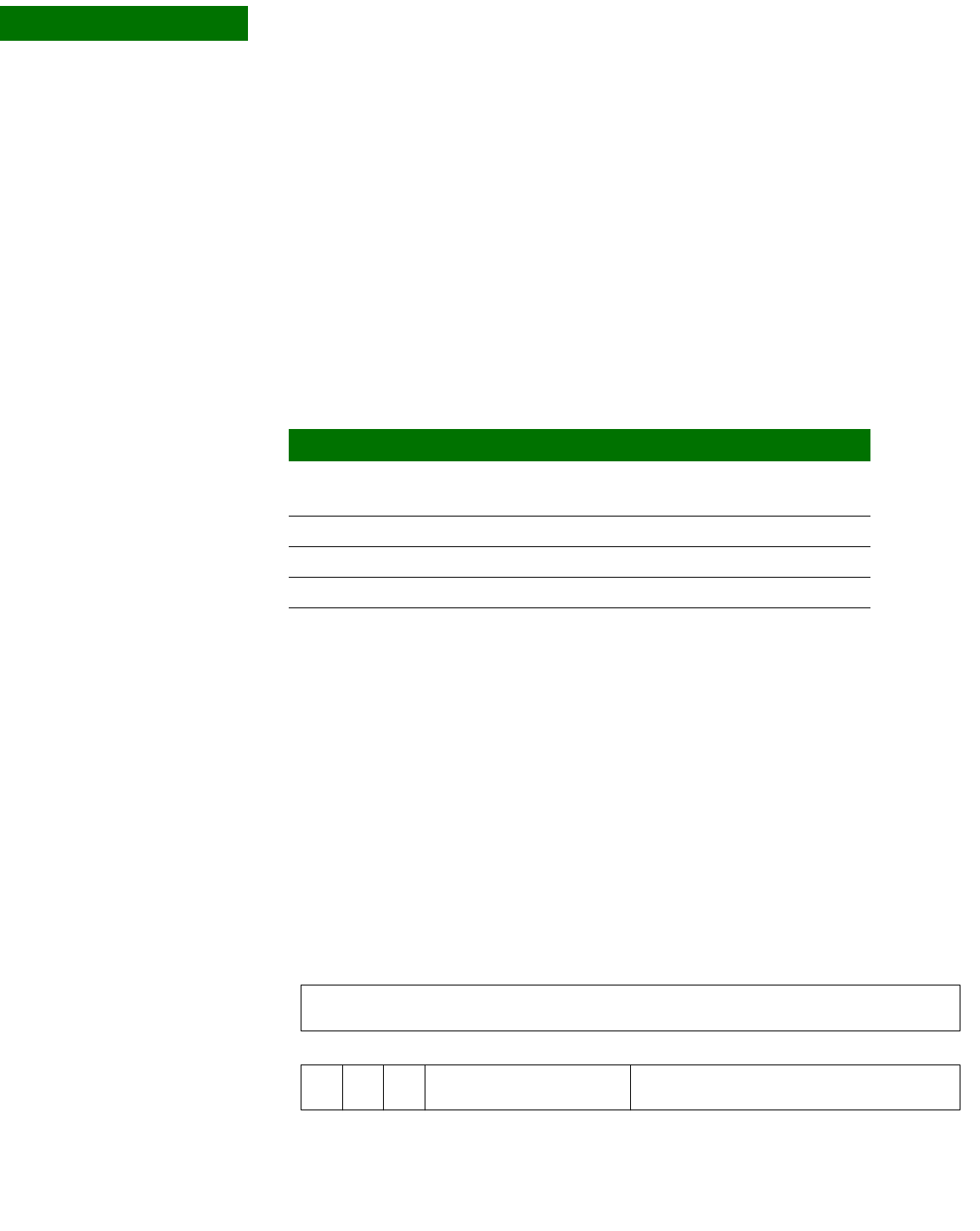

Register address

map

This table shows the register addresses. All configuration registers must be accessed

as 32-bit words and as single accesses only. Bursting is not allowed.

After a reset, all registers are set to the initial value. If an unspecified register or

bit is read, a zero is returned.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Command Transmit Data register

Address: 9005 0000

The Command Transmit Data (

CMD_TX_DATA_REG) register is the primary interface

register for transmission of data between the I/O hub and I

2

C bus. This register is

write only.

Register

Register Description

9005 0000 Command Transmit Data register (

CMD_TX_DATA_REG)

Status Receive Data register (STATUS_RX_DATA_REG)

9005 0004 Master Address register

9005 0008 Slave Address register

9005 000C Configuration register

TXVAL CMD TXDATA

13121110987654321015

14

PIPE DLEN

31

29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved