ETHERNET COMMUNICATION MODULE

Transmit packet processor

270 Hardware Reference NS9215

reside in different buffers in system memory, several buffer descriptors can be used

to transfer the frame.

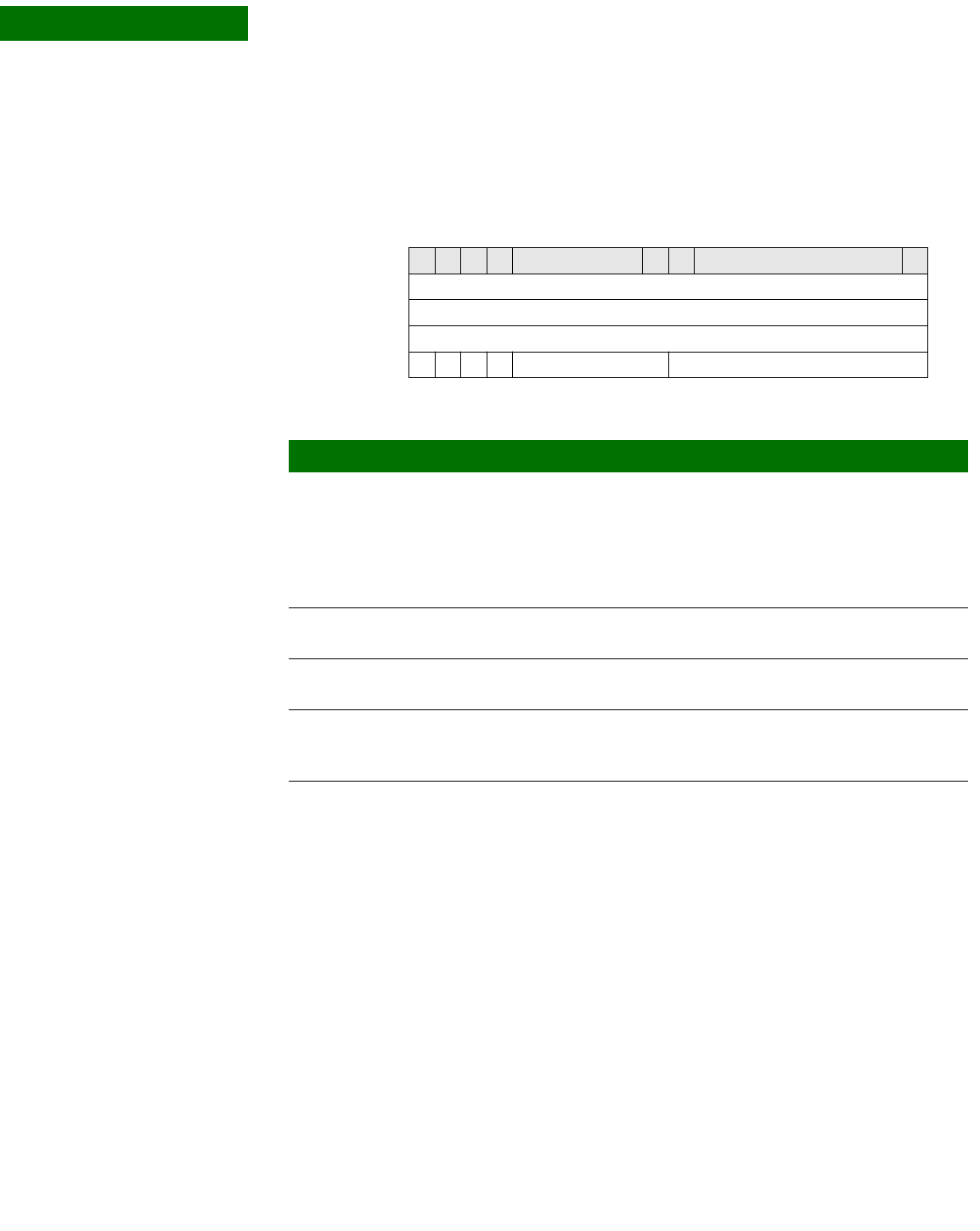

Transmit buffer

descriptor format

All buffer descriptors (that is, up to 64) are found in a local TX buffer descriptor

RAM. This is the transmit buffer descriptor format.

Transmit buffer

descriptor field

definitions

Destination Address (not used)

Buffer Length (11-bits used)

Status

Source Address

0

OFFSET + 0

OFFSET + 4

OFFSET + 8

OFFSET + C

FILW Reserved

31 151630 29 28

Field Description

W

WRAP bit, which, when set, tells the TX_WR logic that this is the last buffer descriptor

within the continuous list of descriptors in the TX buffer descriptor RAM. The next

buffer descriptor is found using the initial buffer descriptor pointer in the TX Buffer

Descriptor Pointer register (TXPTR).

When the

WRAP bit is not set, the next buffer descriptor is located at the next entry

in the TX buffer descriptor RAM.

I When set, tells the

TX_WR logic to set TXBUFC in the Ethernet Interrupt Status

register when the buffer is closed due to a normal channel completion.

Buffer pointer 32-bit pointer to the start of the buffer in system memory. This pointer can be aligned

on any byte of a 32-bit word.

Status Lower 16 bits of the Ethernet Transmit Status register. The status is returned from

the Ethernet MAC at the end of the frame and written into the last buffer descriptor

of the frame.

L When set, tells the

TX_WR logic that this buffer descriptor is the last descriptor that

completes an entire frame. This bit allows multiple descriptors to be chained together

to make up a frame.