. . . . .

SERIAL CONTROL MODULE: HDLC

Normal mode operation

www.digiembedded.com 421

only uses the clock transitions to track the bit-cell boundaries, by ignoring all

transitions occurring outside a window around the center of the bit-cell. The window

is half a bit-cell wide.

Because the clock transitions are guaranteed, the DPLL requires that they always be

present. If no transition is found in the window around the center of the bit-cell for

two successive bit-cells, the DPLL is not in lock and immediately enters search

mode. Search mode presumes that the next transition seen is a clock transition and

immediately synchronizes to this transition. No clock output is provided to the

receiver during the search operation.

Biphase-Mark

and Biphase-

Space encoding

Biphase-mark and biphase-space encoding are identical per the DPLL and are similar

to biphase-level. The primary difference is the clock placement and data

transitions. With these encodings, the clock transitions are at the bit-cell boundary

and the data transitions are at the center of the bit-cell; the DPLL operation is

adjusted accordingly. Decoding biphase-mark or biphase-space encoding requires

that the data be sampled by both edges of the recovered receive clock.

IRDA-compliant

encode

There is an optional IRDA-compliant encode and decode function available. The

encoder sends an active-high pulse for a zero and no pulse for a one. The pulse is

1/4th of a bit-cell wide. The decoder watches for active-low pulses which are

stretched to one bit time wide to recreate the normal asynchronous waveform for the

receiver. enabling the IRDA-compliant encode/decode modifies the transmitter so

there are always two opening flags transmitted.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Normal mode operation

The HDLC achieves normal mode operation by programming the HDLC and Wrapper

configuration registers.

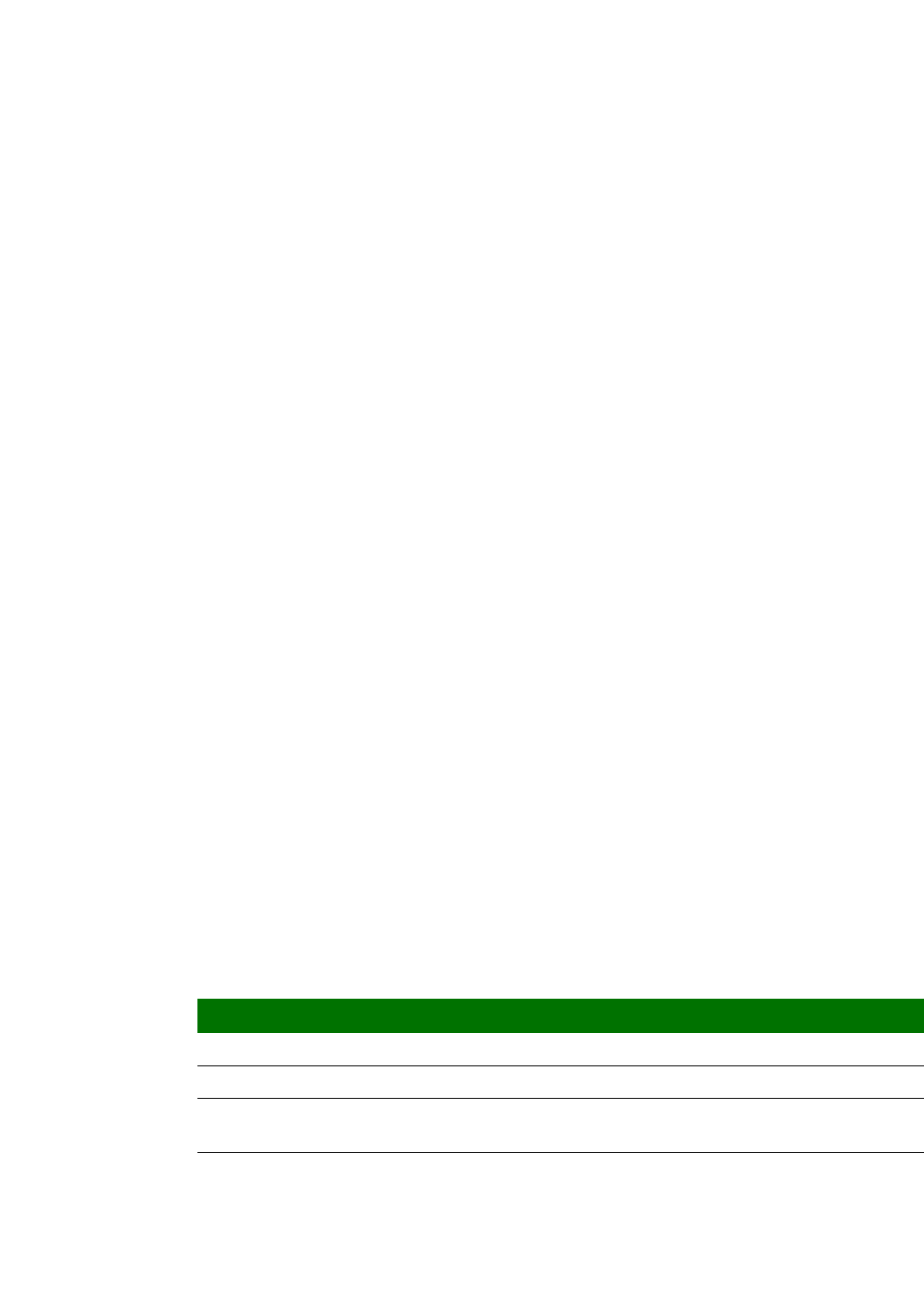

Example

configuration

This example shows a normal mode operation configuration for a typical

application. Any field not specified in this table can be left at reset value.

Control register Field Value Comment

HDLC Control register CLK 0x3 Enable internal clock generation

HDLC Clock Divider High EN 0x1 Enable the internal clock divider; the

clock rate will be 1.8432 Mbps.