. . . . .

SERIAL CONTROL MODULE: HDLC

HDLC Control Register 1

www.digiembedded.com 429

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

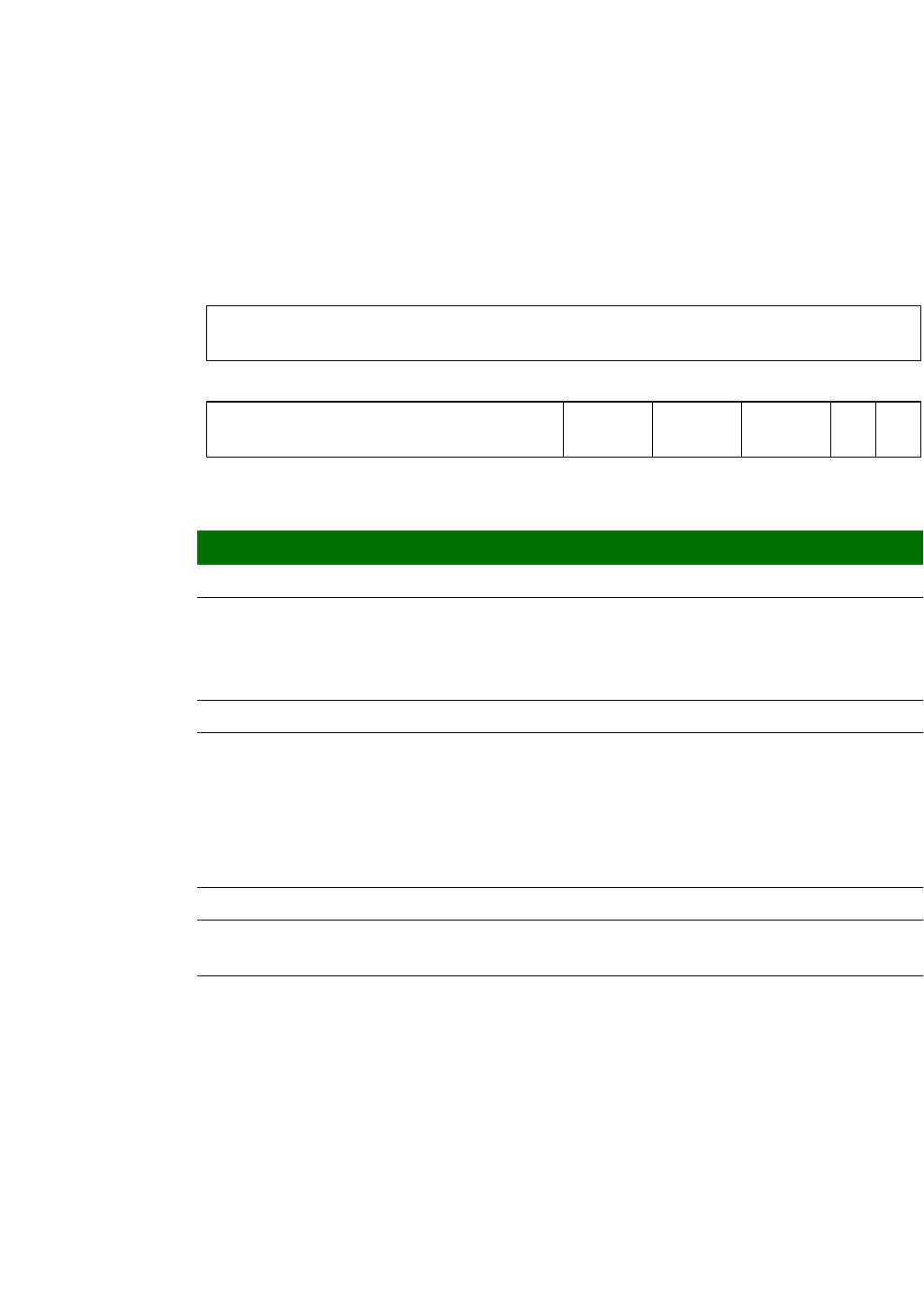

HDLC Control Register 1

Address: 9002_9110

HDLC Control Register 1 configures the HDLC transmitter and receiver.

Register

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

HDLC Control Register 2

Address: 9002_9114

HDLC Control Register 2 configures the HDLC transmitter and receiver.

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved CLK

Reserved

HDATA HDATA

Not

used

HINT

Bits Access Mnemonic Reset Description

D31:08 R Not used 0 Write this field to 0.

D07:06 R HMODE 0 00 Normal operation

01 Force receiver to flag search mode

10 Normal operation

11 Force transmitter to send abort

D05:04 N/A Reserved N/A N/A

D03:02 R/W CLK 0 Clock source

Note: This field should be programmed last

00 Reserved

01 Reserved

10 Use external clock

11 Use internal clock

D01 R/W Not used 0 Always write 0 to this bit.

D00 R/W HINT 0 0 Disable the HDLC interrupt

1 Enable the HDLC interrupt