. . . . .

PINOUT (265)

System reset

www.digiembedded.com 47

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System reset

Pin Signal U/D I/O OD Description

E12 reset_n U I System reset

A5 reset_out_n O 2 System reset output

A13 reset_done O 2 Reset done

D9 sreset_n U I Soft system reset

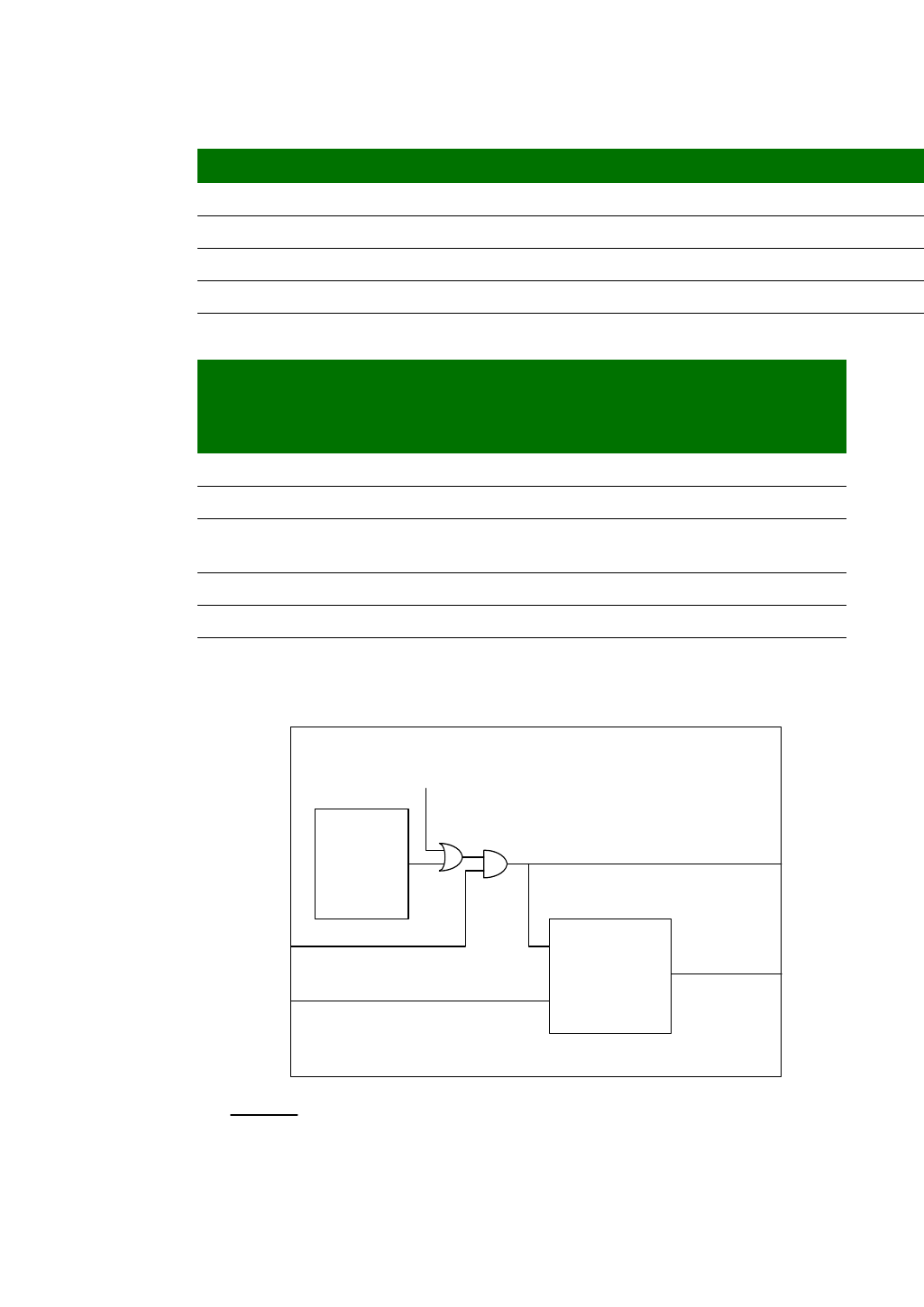

RESET_n

pin

SRESET_n

pin

PLL Config

Reg.

Update

Watchdog

Time-Out

Reset

SPI YES YES YES YES

BootStrapping PL YES NO NO NO

Other Strappings

(Endianess

YESNONONO

GPIO Configuration YES NO NO NO

Other (ASIC) Registers YES YES YES YEs

POR

trips when

voltage on L3

drops below

2.74V/2.97V

POR disable

(as encoded on mode pins)

NS9215 Core

NS9215

reset_out_n

reset_done

reset_n

sreset_n

Definitions

reset_n – hardware reset input buffer with pull-up resistor

sreset_n – soft reset input buffer with pull-up resistor, does not reset the PLL

reset_out_n – hardware reset to NS9215 core and output buffer, resets all logic in NS9215 core including PLL

reset_done – reflects the state of the ARM926 reset, for any type of reset event