ETHERNET COMMUNICATION MODULE

RX Free Buffer register

326 Hardware Reference NS9215

Register

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RX Free Buffer register

Address: A060 0A3C

So the

RX_RD logic knows when the software is freeing a buffer for reuse, the

software writes to the RXFREE register each time it frees a buffer in one of the

pools. RXFREE has an individual bit for each pool; this bit is set to 1 when the

register is written. Reads to RXFREE always return all 0s.

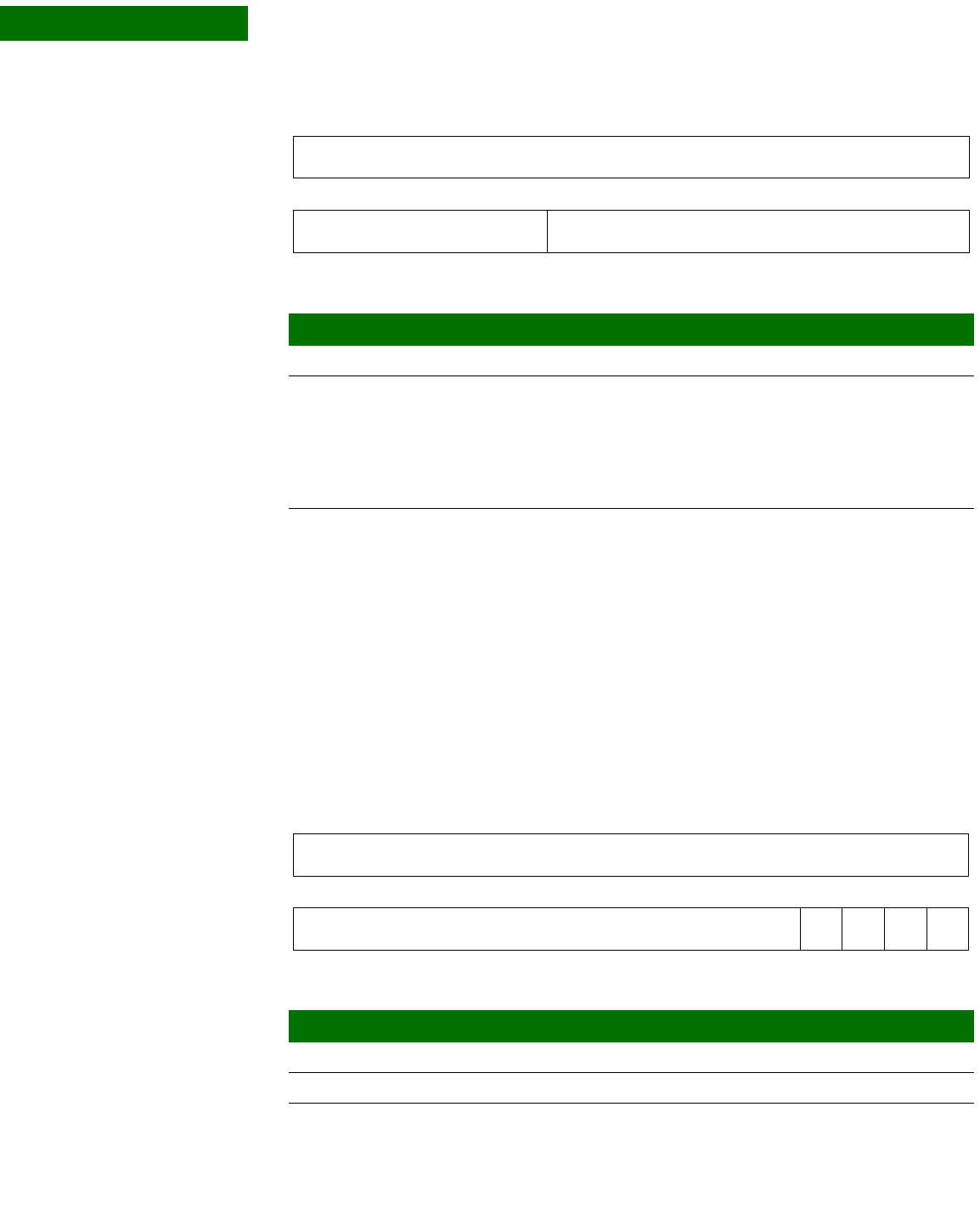

Register

Register bit

assignment

Reserved

TXOFF

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved

Bits Access Mnemonic Reset Description

D31:10 N/A Reserved N/A N/A

D09:00 R TXOFF 0x000 Contains a 10-bit byte offset from the start of the transmit

ring in the TX buffer descriptor RAM. The offset is

updated at the end of the TX packet, and will have the

offset to the next buffer descriptor that will be used.

TXOFF can be used to determine from where the

TX_WR

logic will grab the next packet.

Reserved

RX

FREED

RX

FREEA

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved

RX

FREEC

RX

FREEB

Bits Access Mnemonic Reset Description

D31:04 N/A Reserved N/A N/A

D03 W RXFREED 0 Pool D free bit

D02 W RXFREEC 0 Pool C free bit