SYSTEM CONTROL MODULE

General Arbiter Control register

158 Hardware Reference NS9215

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

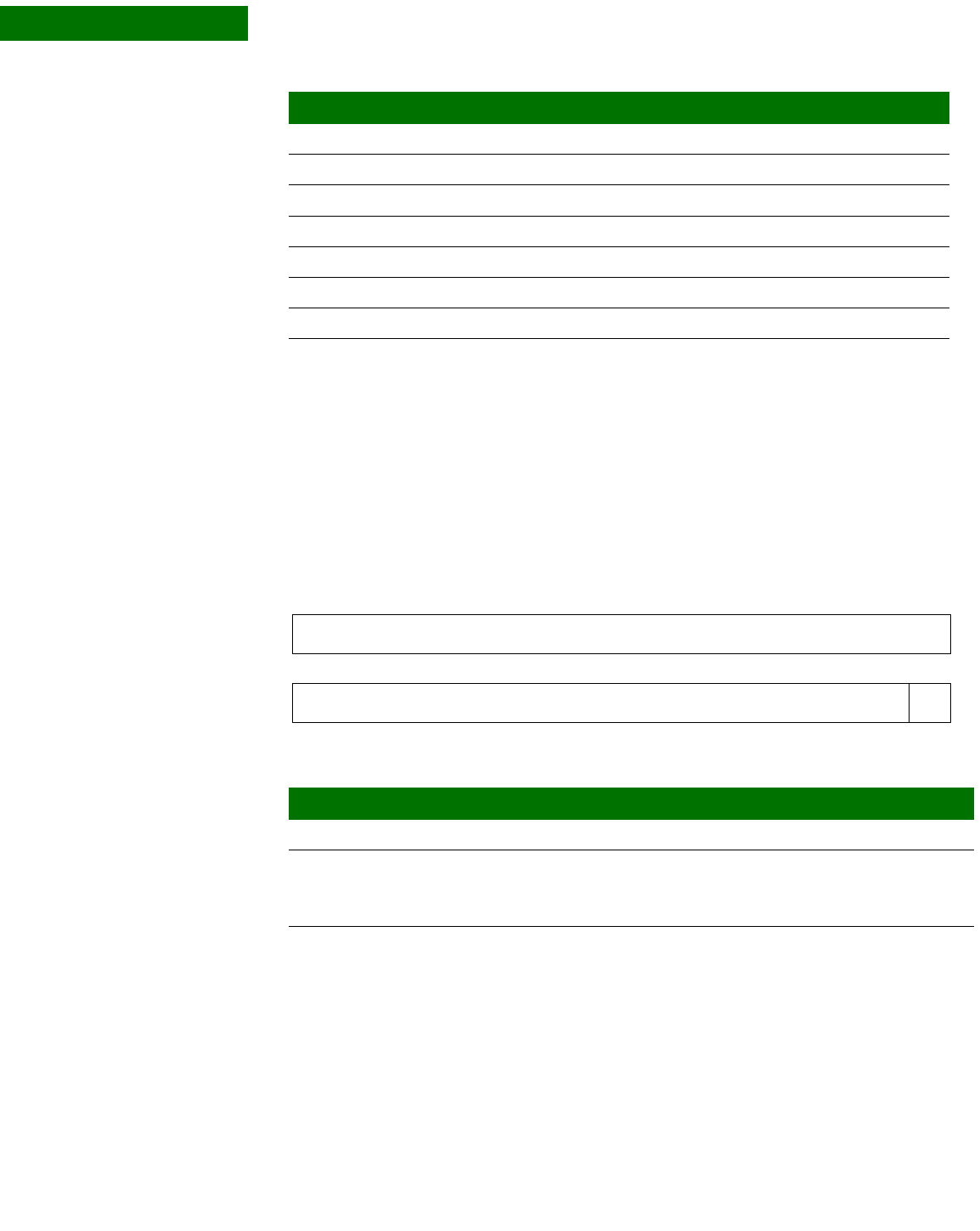

General Arbiter Control register

Address: A090 0000

The General Arbiter Control register controls whether the CPU access is routed

through the main arbiter or is connected directly to the memory controller.

Register

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

BRC0, BRC1, BRC2, and BRC3 registers

Addresses: A090 0004 / 0008 / 000C / 0010

The BRC[0:3] registers control the AHB arbiter bandwidth allocation scheme.

A090 0214 External Interrupt 0 Control register

A090 0218 External Interrupt 1 Control register

A090 021C External Interrupt 2 Control register

A090 0220 External Interrupt 3 Control register

A090 0224 RTC Module Control

A090 0228 Power Management

A090 022C AHB Bus Activity Status

Offset [31:24] [23:16] [15:8] [7:0]

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved

Reserved

Arb

Control

Bits Access Mnemonic Reset Description

D31:01 N/A Reserved N/A N/A

D00 R ArbControl 0x0 Arbiter control

0 CPU connected directly to memory controller

1 CPU connected to main arbiter