. . . . .

ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

ADC Clock Configuration register

www.digiembedded.com 477

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ADC Clock Configuration register

Address: 9003_9004

The ADC Clock Configuration register controls the ADC clock generator. The source

clock is the output of the PLL. The maximum ADC clock frequency is 14 MHz and the

conversion time is 14 clock cycles. This is the formula for the ADC clock:

ADC clock = PLL clock / (2 x (N+1))

Example

PLL clock frequency = 299.8272 MHz

N value = 10

ADC clock frequency:

ADC clock = 299.8272 MHz / (2 x (10+1)) = 13.6285 MHz

Wait states can be added to increase conversion time beyond 14 clock cycles.

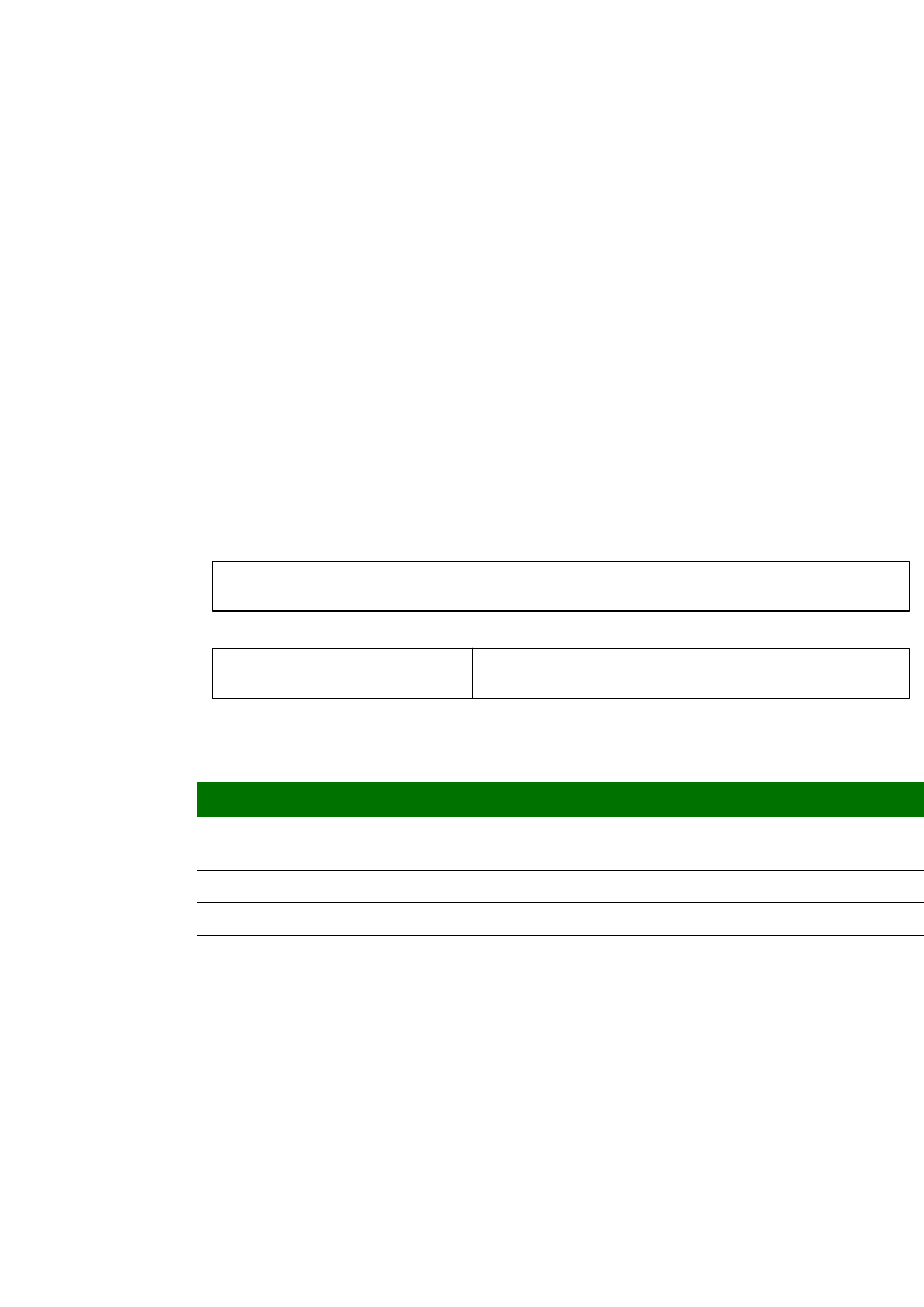

Register

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ADC Output Registers 0-7

Addresses: 9003_9008 / 9003_900C / 9003_9010 / 9003_9014 / 9003_9018 /

9003_901C / 9003_9020 / 9003_9024

The ADC Output registers provide CPU access for the ADC output for each channel.

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

WAIT

N

Not used

Bit(s) Access Mnemonic Reset Description

D31:16 R/W WAIT N/A Number of additional clock cycles per conversion

cycle.

D15:10 R/W Not used 0 This field must be written to 0.

D09:00 R/W N 0 ADC clock converter.