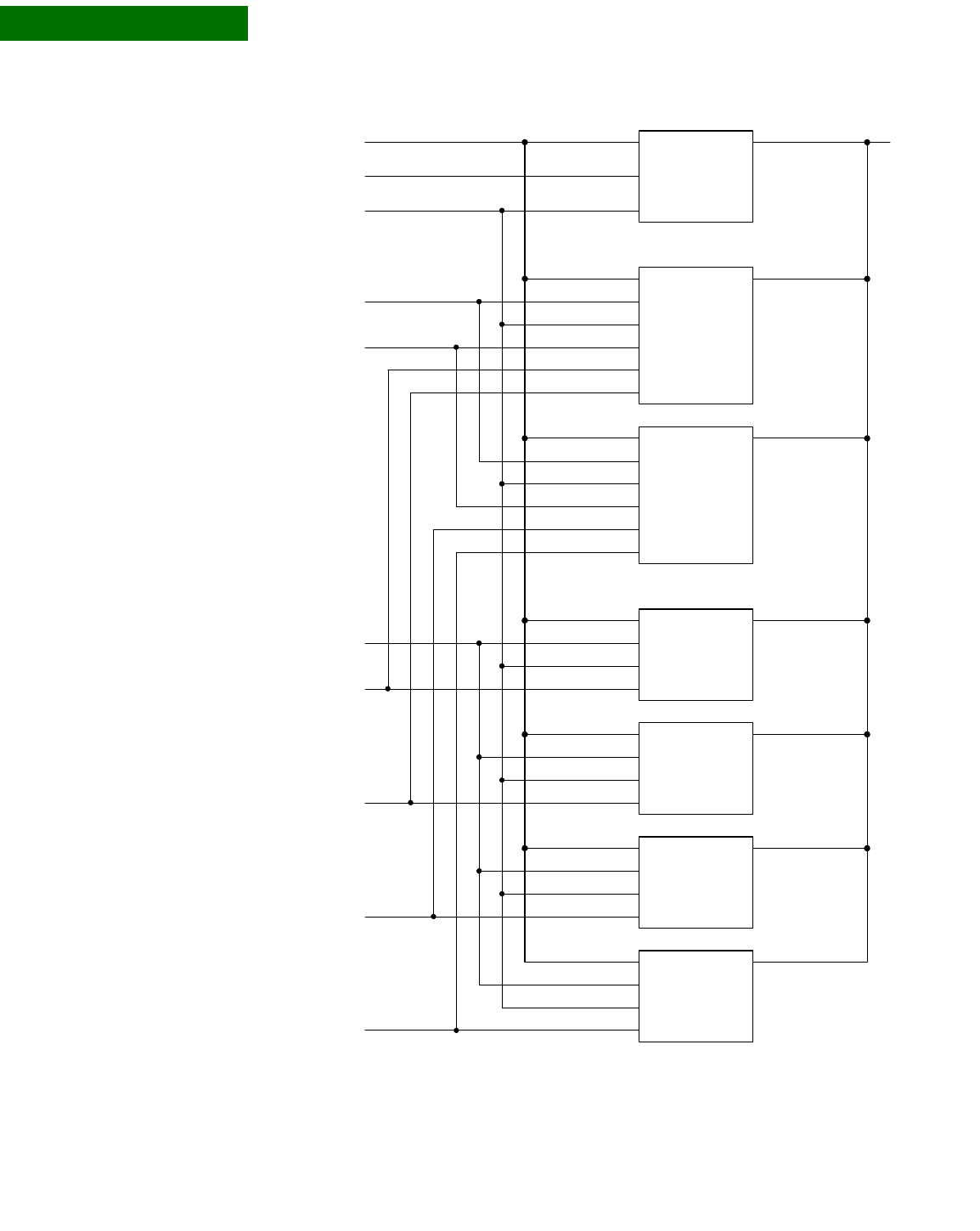

MEMORY CONTROLLER

Address connectivity

224 Hardware Reference NS9215

datat[31:0]

data[31:0]

data[31:16]

data[15:0]

data[31:24]

data[23:16]

data[15:8]

data[7:0]

Q[31:0]

2Mx32 ROM

64Kx16 SRAM

128Kx8 SRAM

A[15:0]

CE_n

OE_n

WE_n

UB_n

LB_n

IO[15:0]

A[15:0]

CE_n

OE_n

WE_n

UB_n

LB_n

IO[15:0]

A[16:0]

CE_n

OE_n

WE_n

IO[7:0]

A[16:0]

CE_n

OE_n

WE_n

IO[7:0]

A[16:0]

CE_n

OE_n

WE_n

IO[7:0]

A[16:0]

CE_n

OE_n

WE_n

IO[7:0]

addr[22:2]

addr[11:2]

addr[17:2]

addr[18:2]

addr[18:2]

addr[18:2]

addr[18:2]

A[20:0]

CE_n

OE_n

addr[22:0]

cs[0]

st_oe_n

cs[1]

st_we_n

cs[2]

data_mask[3]

data_mask[2]

data_mask[1]

data_mask[0]