ETHERNET COMMUNICATION MODULE

TX Buffer Descriptor Pointer register

320 Hardware Reference NS9215

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

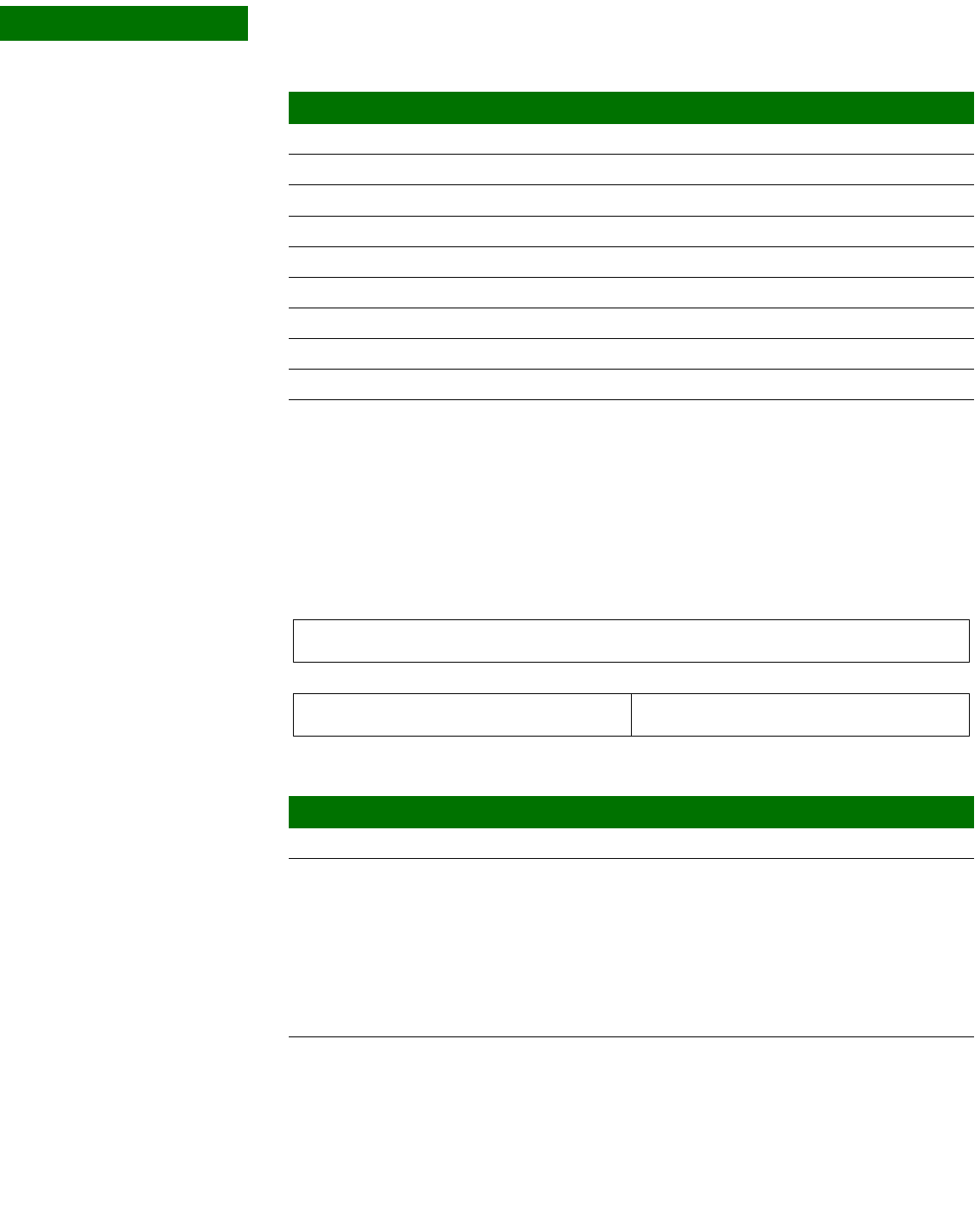

TX Buffer Descriptor Pointer register

Address: A060 0A18

Register

Register bit

assignment

D16 R/W EN_RXBR 0 Enable the RXBR interrupt bit.

D15:07 N/A Reserved N/A N/A

D06 R/W EN_STOVFL 0 Enable the STOVFL interrupt bit.

D05 R/W Not used 0 Always write as 0.

D04 R/W EN_TXBUFC 0 Enable the TXBUFC interrupt bit.

D03 R/W EN_TXBUFNR 0 Enable the TXBUFNR interrupt bit.

D02 R/W EN_TXDONE 0 Enable the TXDONE interrupt bit.

D01 R/W EN_TXERR 0 Enable the TXERR interrupt bit.

D00 R/W EN_TXIDLE 0 Enable the TXIDLE interrupt bit.

Bits Access Mnemonic Reset Description

Reserved

TXPTR

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved

Bits Access Mnemonic Reset Description

D31:08 N/A Reserved N/A N/A

D07:00 R/W TXPTR 0x00 Contains a pointer to the initial transmit buffer descriptor

in the TX buffer descriptor RAM.

Note: This pointer is the 8-bit physical address of the

TX buffer descriptor RAM, and points to the

first location of the four-location buffer

descriptor. The byte offset of this buffer

descriptor can be calculated by multiplying this

value by 4.