SYSTEM CONTROL MODULE

Timer Master Control register

162 Hardware Reference NS9215

Register

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer Master Control register

Address: A090 0024

The Timer Master Control register resets and enables the timer in groups, which is

useful when using the timers in PW applications.

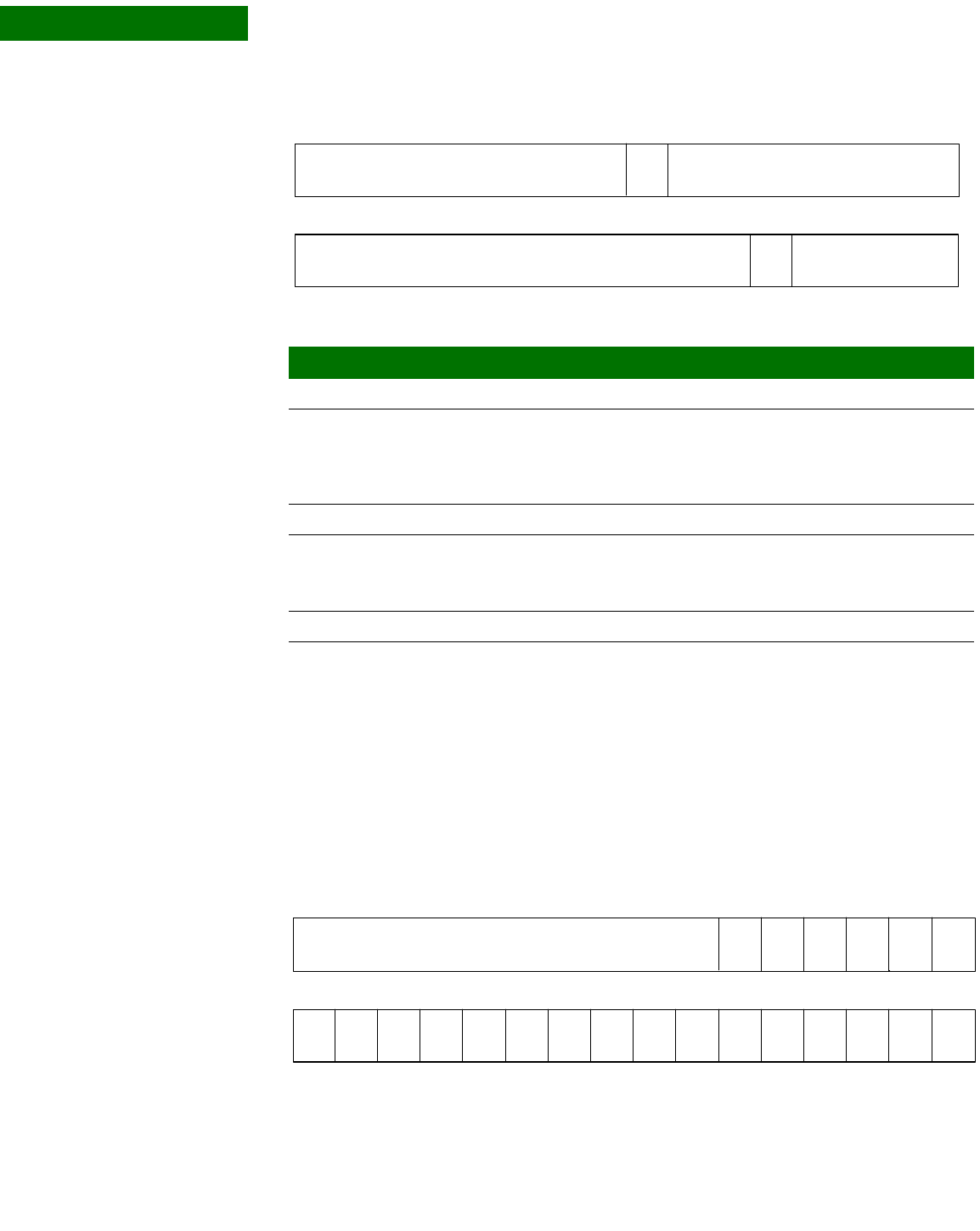

Register

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved

Reserved

Reserved

EIC

Reserved

SERDC

Bits Access Mnemonic Reset Description

D31:24 N/A Reserved N/A N/A

D23 R/W EIC 0x0 AHB Error Interrupt Clear

Write a 1, then a 0 to this register to clear the AHB

error interrupt and to clear the AHB Error Detect

Status 1 and AHB Error Detect Status 2 registers.

D22:05 N/A Reserved N/A N/A

D04 R/W SERDC 0x0 AHB Slave Error Response Detect Config

0 Record error only

1 Generate IRQ

D03:00 N/A Reserved N/A N/A

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

T6HSE

Reserved

T1E

T8RSE

T9HSE

T4E

T9RSE T9LSE T8LSE T8HSE

T7RSE T7LSE T7HSE T6RSE T6LSE T9E T8E T7E T6E T5E T3E T2E

T0E