SERIAL CONTROL MODULE: HDLC

Digital phase-locked-loop (DPLL) operation: Encoding

418 Hardware Reference NS9215

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Digital phase-locked-loop (DPLL) operation: Encoding

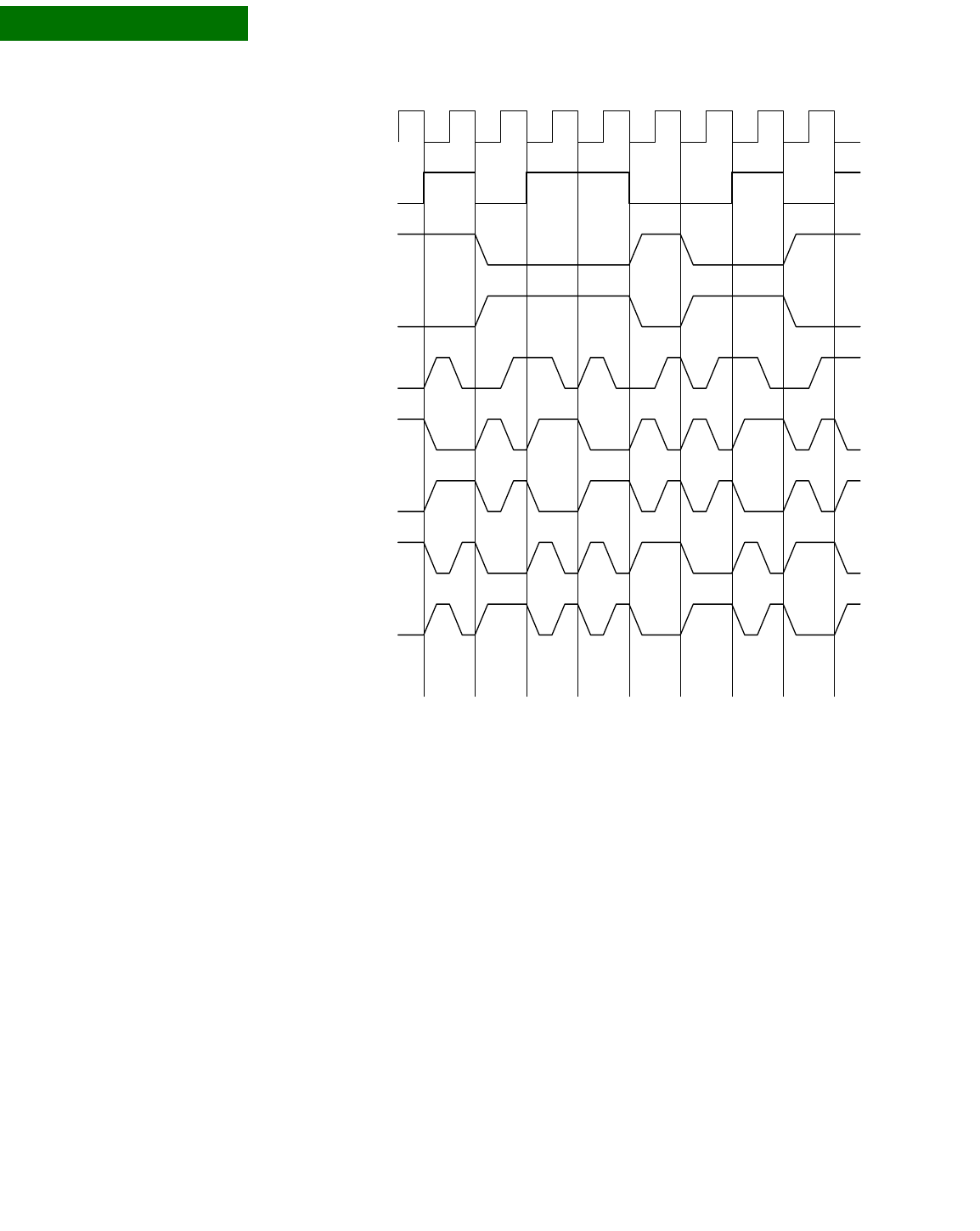

In the HDLC module, the internal clock comes from the output of the dedicated

divider. The divider output is divided by 16 to form the transmit clock and is fed to

the DPLL to form the receive clock. The DPLL basically is a divide-by-16 counter

that uses the transition timings on the receive data stream to adjust its count. The

DPLL adjusts the count so the DPLL output is placed properly in the bit cells to

sample the receive data.

Transitions To work properly, the receive data stream requires transitions. NRZ data encoding

does not guarantee transitions in all cases (for example, a long string of zeroes), but

the other data encodings do. NRZI guarantees transitions because of inserted zeroes.

The Biphase encodings all have at least one transition per bit cell.

NRZ Data

HDLC Clock

NRZI

NRZI

Biphase-Level

Biphase-Space

Biphase-Space

Biphase-Mark

Biphase-Mark

data 10100110