. . . . .

ETHERNET COMMUNICATION MODULE

Collision Window/Retry register

www.digiembedded.com 293

Register bit assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Collision Window/Retry register

Address: A060 0410

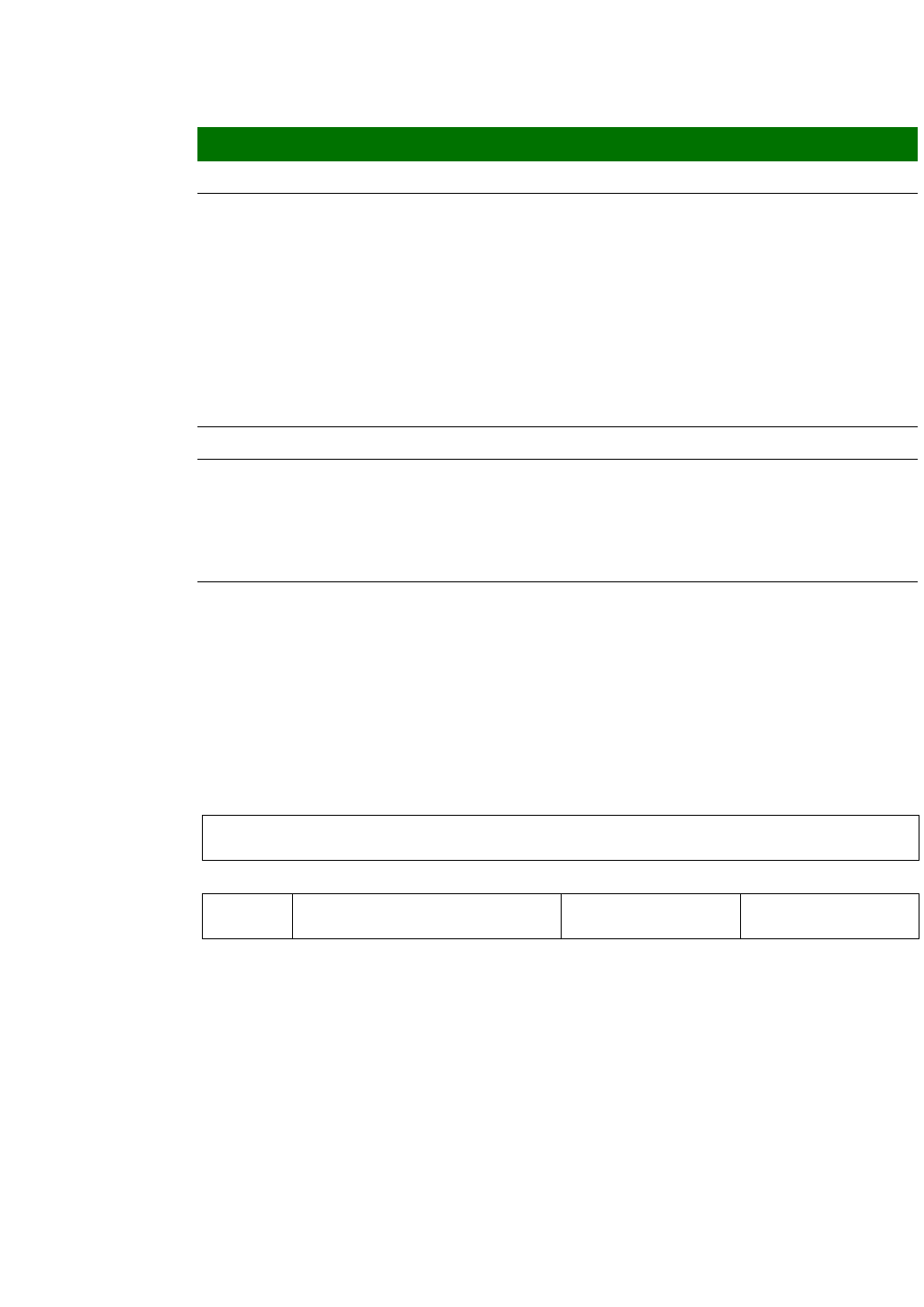

Register

Bits Access Mnemonic Reset Description

D31:15 N/A Reserved N/A N/A

D14:08 R/W IPGR1 0x00 Non back-to-back inter-packet-gap part 1

Programmable field indicating optional carrierSense

window (referenced in IEEE 8.2.3/4.2.3.2.1).

If carrier is detected during the timing of IPGR1, the

MAC defers to carrier.

If carrier comes after IPGR1, the MAC continues

timing IPGR2 and transmits — knowingly causing

a collision. This ensures fair access to the medium.

IPGR1’s range of values is

0x0 to IPGR2. The

recommended value is

0xC.

D07 N/A Reserved N/A N/A

D06:00 R/W IPGR2 0x00 Non back-to-back inter-packet-gap part 2

Programmable field indicating the non back-to-back

inter-packet-gap. The recommended value for this field

is

0x12 (18d), which represents the minimum IPG of 0.96

μS in 100 Mbps or 9.6 μS in 10 Mbps.

Reserved

RETX

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

CWINReserved Reserved