. . . . .

SERIAL CONTROL MODULE: HDLC

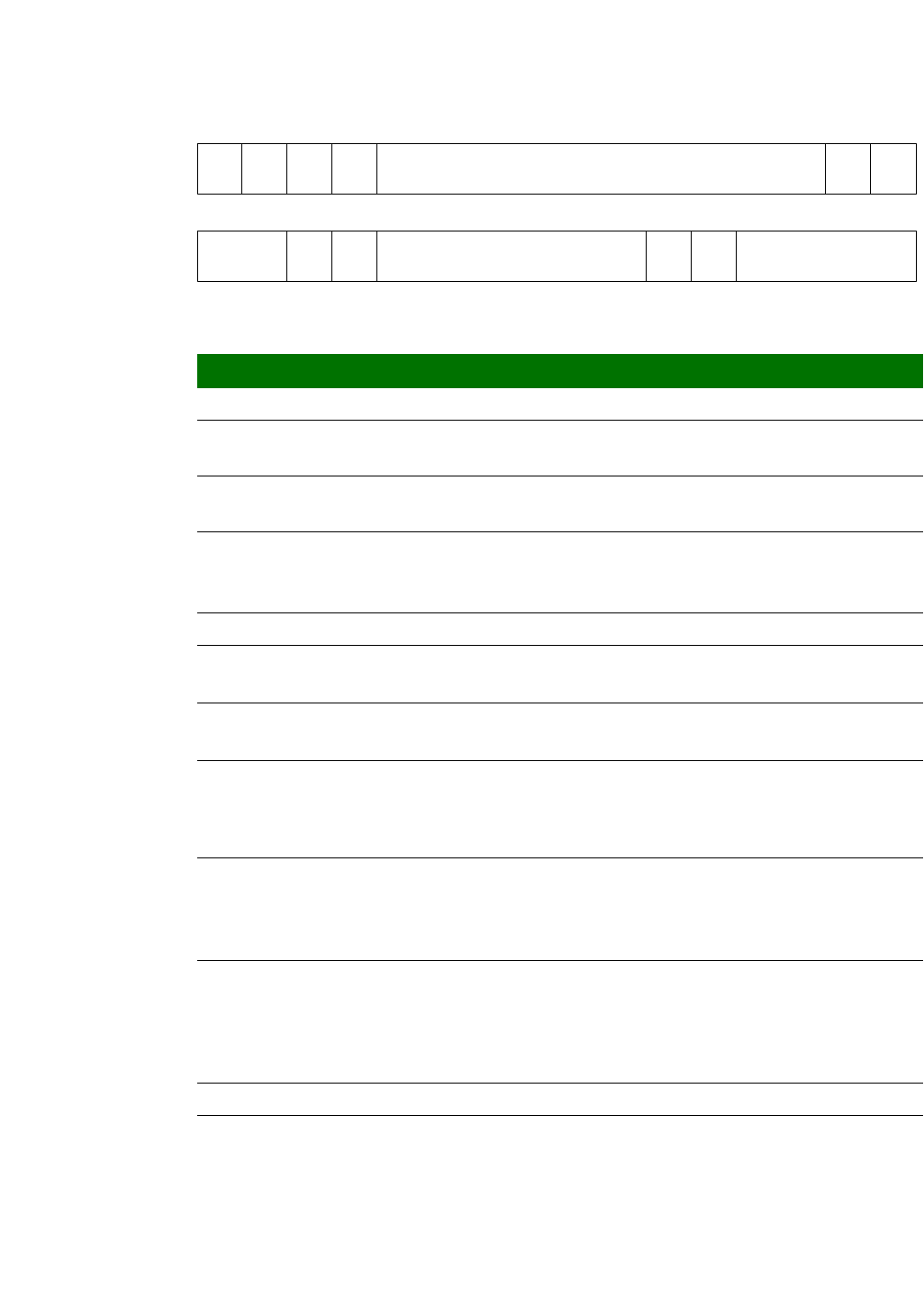

Wrapper Configuration register

www.digiembedded.com 423

Register

Register bit

assignment

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved

Reserved

ReservedLLRLCRC

RX

CLOSE

RXBYTES

Reserv

ed

RXEN TXEN MODE

RX

FLUSH

TX

FLUSH

Bits Access Mnemonic Reset Description

D31 N/A Reserved N/A N/A

D30 R/W RXEN 0 0 Disable wrapper function

1 Enable wrapper to process receive characters

D29 R/W TXEN 0 0 Disable wrapper transmitter function

1 Enable wrapper to process transmit characters

D28 R/W MODE 0 Applies only to UART channel C.

0 UART mode

1 HDLC mode

D27:18 N/A Reserved N/A N/A

D17 R/W RXFLUSH 0 Resets the contents of the 64-byte RXFIFO.

Write a 1, then a 0 to reset the FIFO.

D16 R/W TXFLUSH 0 Resets the contents of the 64-byte TX FIFO.

Write a 1, then a 0 to reset the FIFO.

D15:14 R RXBYTES 00 Indicates how many bytes are pending in the wrapper.

The wrapper writes to the RX FIFO only when 4 bytes are

received or a buffer close event occurs, such as end of

frame.

D13 R/W RXCLOSE 0 Allows software to close a receive buffer. Hardware

clears this bit when the buffer has been closed.

0 Idle or buffer already closed

1 Software initiated buffer close

D12 R/W CRC 0 Controls whether the HDLC transmitter hardware sends

CRC bytes before the closing flag.

0 Send CRC bytes before the closing flag

1 Do not send CRC bytes before the closing flag;

handled by software

D11:06 N/A Reserved 0 N/A

D05 R/W RL 0 Remote loopback

Provides an internal remote loopback feature. When the

RL field is set to 1, the receive HDLC data signal is

connected to the transmit HDLC data signal.