ETHERNET COMMUNICATION MODULE

MII Management Write Data register

298 Hardware Reference NS9215

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MII Management Write Data register

Address: A060 042C

Register

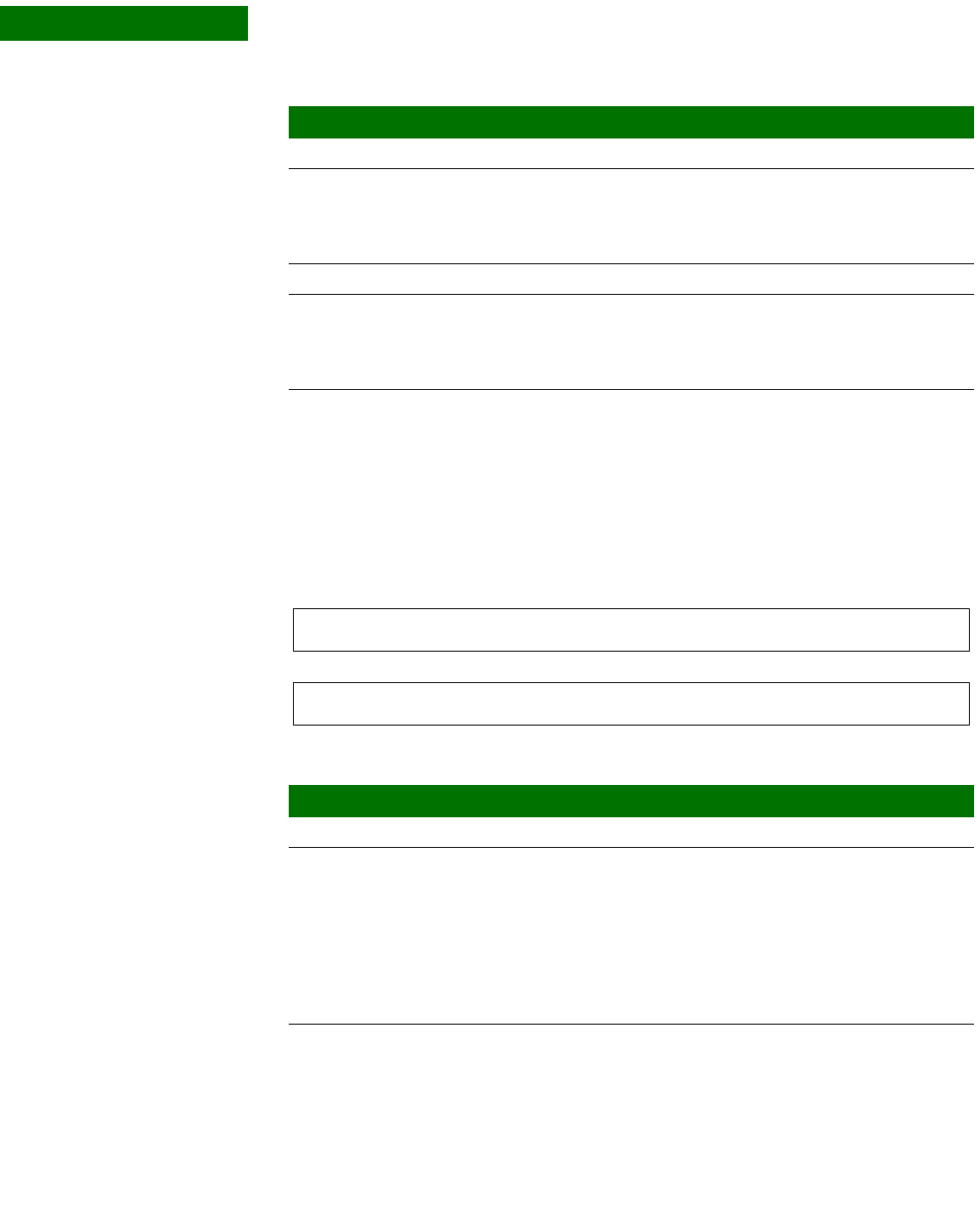

Register bit

assignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MII Management Read Data register

Address: A060 0430

Bits Access Mnemonic Reset Description

D31:13 N/A Reserved N/A N/A

D12:08 R/W DADR 0x00 MII PHY device address

Represents the 5-bit PHY device address field for

management cycles. Up to 32 different PHY devices

can be addressed.

D07:05 N/A Reserved N/A N/A

D04:00 R/W RADR 0x00 MII PHY register address

Represents the 5-bit PHY register address field for

management cycles. Up to 32 registers within a single

PHY device can be addressed.

Reserved

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

MWTD

Bits Access Mnemonic Reset Description

D31:16 N/A Reserved N/A N/A

D15:00 R/W MWTD 0x0000 MII write data

When this register is written, an MII Management

write cycle is performed using this 16-bit data along

with the preconfigured PHY device and PHY register

addresses defined in the MII Management Address

register. The write operation completes when the

BUSY bit in the MII Management Indicators register

returns to 0.