. . . . .

MEMORY CONTROLLER

Static Memory Extended Wait register

www.digiembedded.com 247

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Static Memory Extended Wait register

Address: A070 0080

The Static Memory Extended Wait register times long static memory read and write

transfers (which are longer than can be supported by the Static Memory Read Delay

registers or the Static Memory Write Delay registers) when the EW (extended wait)

bit in the related Static Memory Configuration register is enabled.

There is only one Static Memory Extended Wait register, which is used by the

relevant static memory chip select if the appropriate EW bit is set in the Static

Memory Configuration register.

It is recommended that this register be modified during system initialization, or

when there are no current or outstanding transactions. If necessary, however, these

control bits can be changed during normal operation.

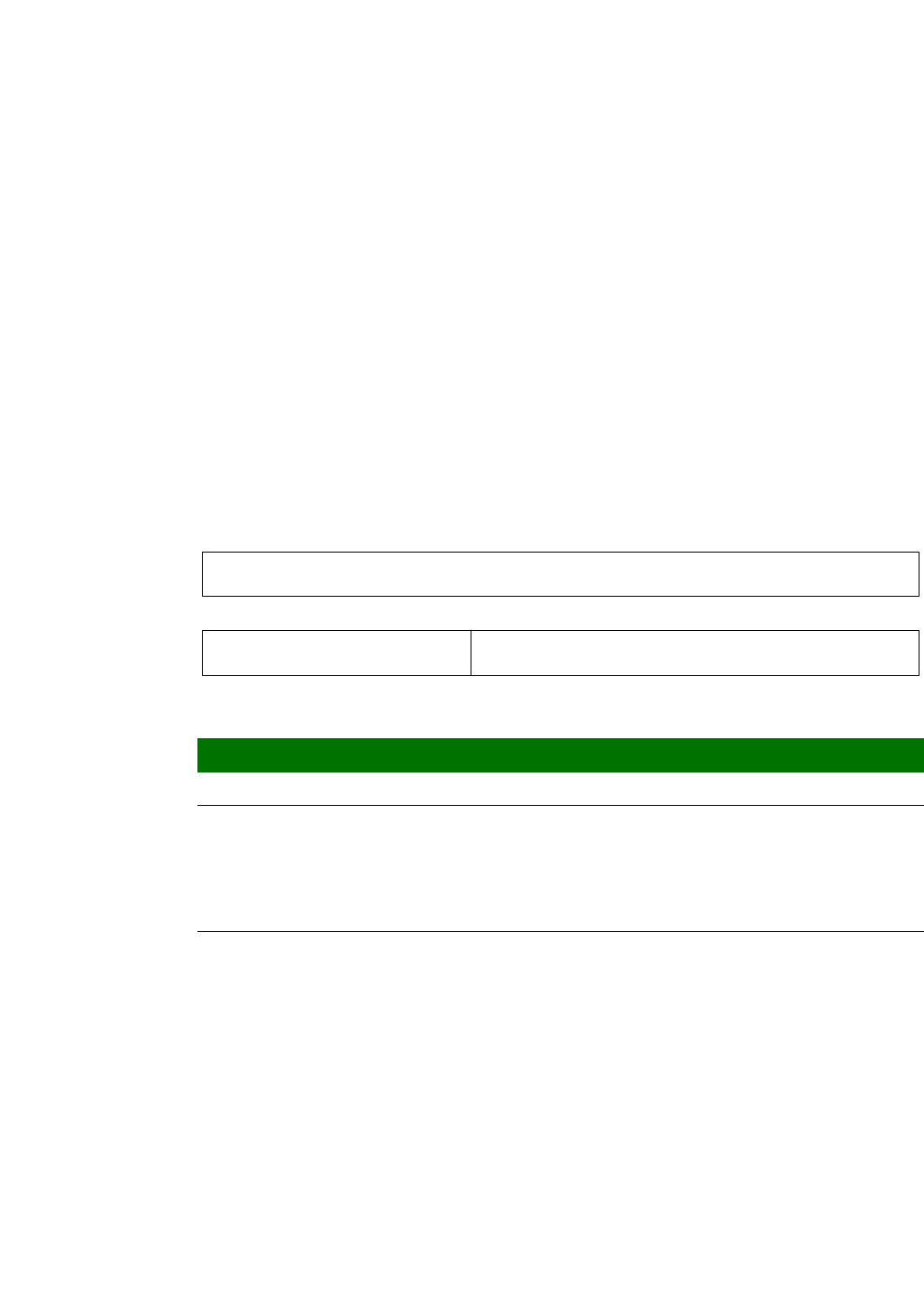

Register

Register bit

assignment

Example

Static memory read/write time = 16 μs

CLK frequency = 50 MHz

This value must be programmed into the Static Memory Extended Wait register:

(16 x 10

-6

x 50 x 10

6

/ 16) - 1 = 49

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Dynamic Memory Configuration 0–3 registers

Address: A070 0100 / 0120 / 0140 / 0160

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved

Reserved EXTW

Bits Access Mnemonic Description

D31:10 N/A Reserved N/A (do not modify)

D09:00 R/W EXTW External wait timeout

0x0

16 clock cycles, where the delay is in clk_out cycles

0x1-0x3FF

(n=1) x 16 clock cycles