114 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

Minimum Issue Latency (without Branch Misprediction) to the minimum branch latency

penalty number from Table 26, which is four cycles.

• Minimum Resource Latency

The minimum cycle distance from the issue clock of the current multiply instruction to the

issue clock of the next multiply instruction assuming the second multiply does not incur a data

dependency and is immediately available from the instruction cache or memory interface.

Example 23 contains a code fragment and an example of computing latencies.

Table 27 shows how to calculate Issue Latency and Result Latency for each instruction. Looking at

the issue column, the UMLAL instruction starts to issue on cycle 0 and the next instruction, ADD,

issues on cycle 2, so the Issue Latency for UMLAL is two. From the code fragment, there is a

result dependency between the UMLAL instruction and the SUB instruction. In Table 27,

UMLAL starts to issue at cycle 0 and the SUB issues at cycle 5; so the Result Latency is 5.

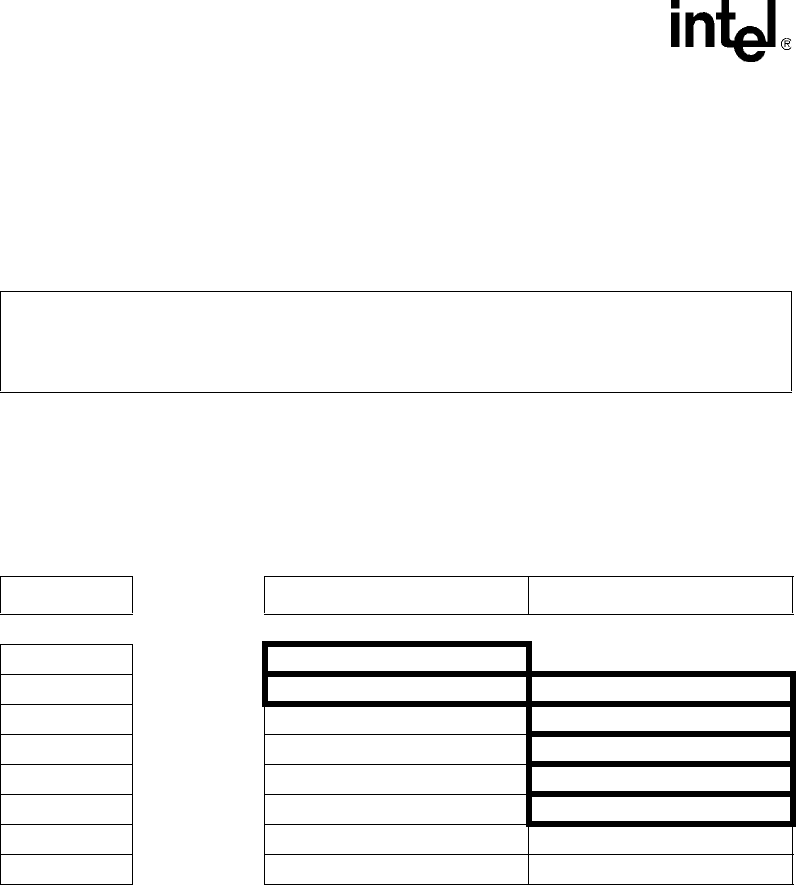

Example 23. Computing Latencies

UMLALr6,r8,r0,r1

ADD r9,r10,r11

SUB r2,r8,r9

MOV r0,r1

Table 27. Latency Example

Cycle Issue Executing

0 umlal (1st cycle) --

1 umlal (2nd cycle) umlal

2 add umlal

3 sub (stalled) umlal & add

4 sub (stalled) umlal

5 sub umlal

6mov sub

7-- mov