140 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

3.12.5 General Purpose I/O (GPIO)

The IXP2800 Network Processor has eight General Purpose Input/Output (GPIO) port pins for use

in generating and capturing application-specific input and output signals. Each pin is

programmable as an input or output or as an interrupt signal sourcing from an external device. The

GPIO can be used with appropriate software in I2C application.

Each GPIO pin can be configured as a input or an output by programming the corresponding GPIO

pin direction register. When programmed as an input, the current state of the GPIO can be read

through the corresponding GPIO pin level register. The register can be read at any time and can be

used to confirm the state of the pin when it is configured as an output. In addition, each GPIO pin

can be programmed to detect a rising or a falling edge by setting the corresponding GPIO rising/

falling edge detect registers.

When configured as an output, the pin can be controlled by writing to the GPIO set register to write

a 1 and by writing to the GPIO clear register to write a 0. These registers can be written regardless

of whether the pin is configured as an input or a output.

Each of the GPIO pins is designed the same and instantiated to the number of GPIO port pins.

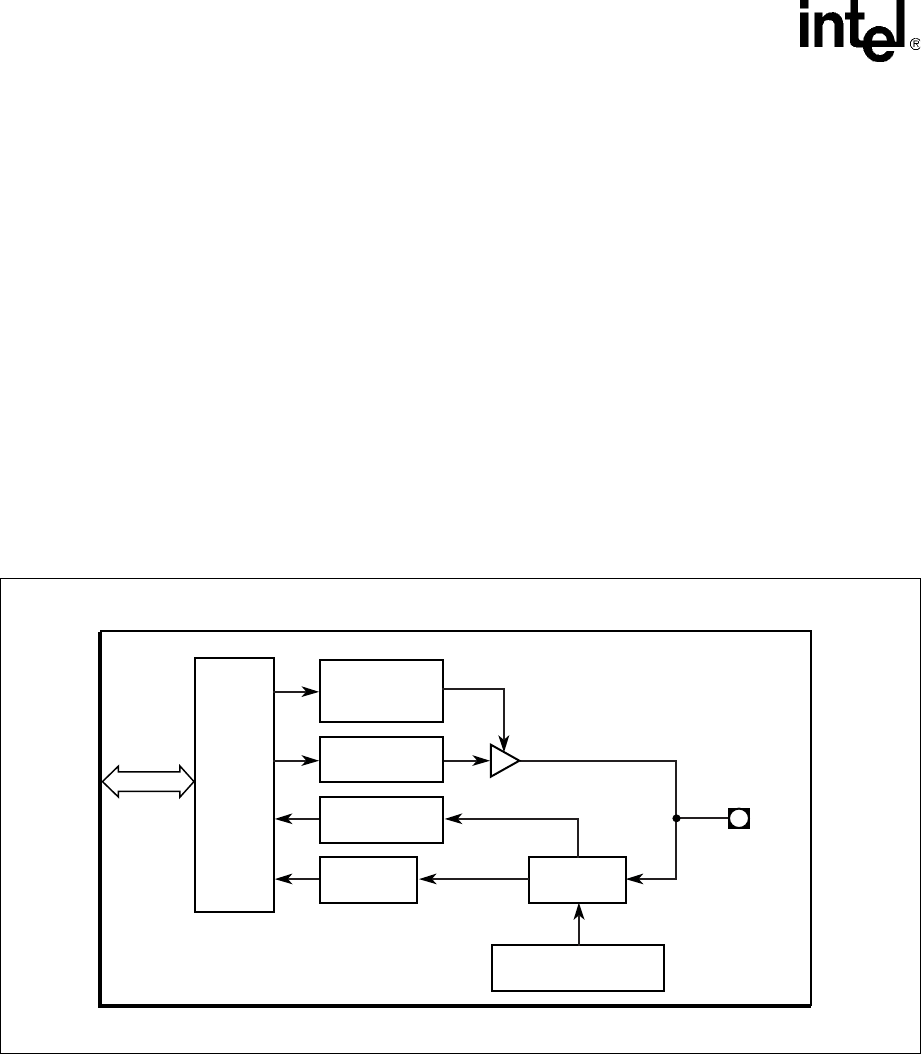

Figure 32 shows a GPIO functional diagram. The GPIO pin as seen can be programmed based on

the configuration registers.

Figure 32. GPIO Functional Diagram

A9701-01

Pin direction

set/clear/prog

register

Pin set/clear/

prog register

Edge detect

status register

Pin Level

Register

Edge detect

logic

GPIO Pin

Rising/Falling edge

detect enable register

Decode

Logic

APB Bus