242 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

The use of some of the receive and transmit pins is based on protocol, SPI-4 or CSIX. For the

LVDS pins, only the active high name is given (for LVDS, there are two pins per signal). The

definitions of the pins can be found in the SPI-4 and CSIX specs, referenced below.

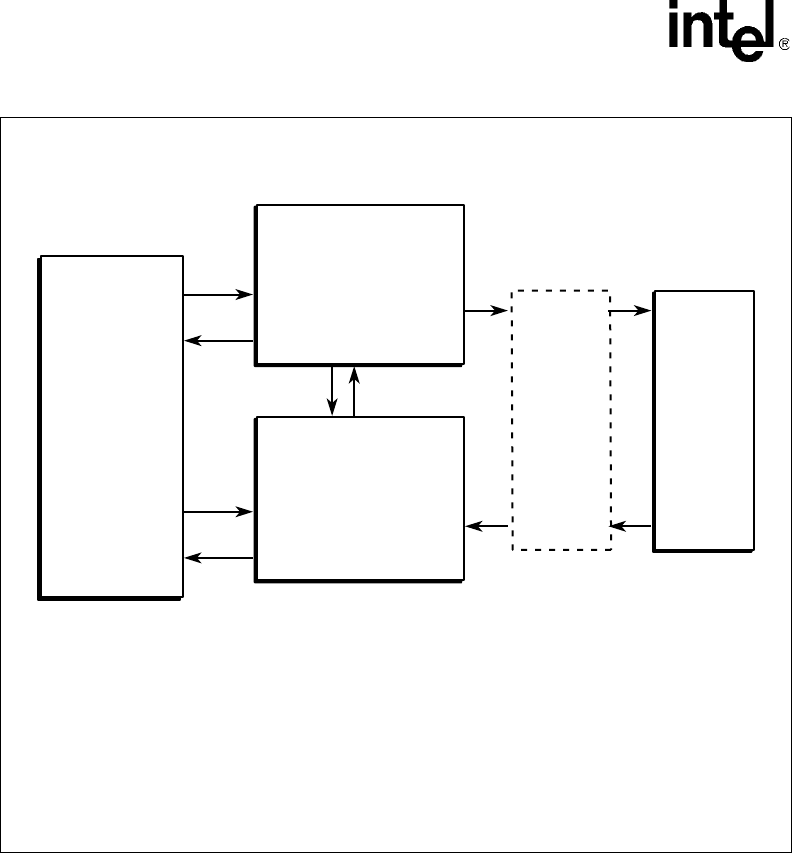

An alternate system configuration is shown in the block diagram in Figure 89. In this case, a single

IXP2800 Network Processor is used for both Ingress and Egress. The bit-rate supported would be

less than in Figure 88. A hypothetical Bus Converter chip, external to the IXP2800 Network

Processor, is used. The block diagram in Figure 89 is only an illustrative example.

Figure 88. Example System Block Diagram

A9759-01

Ingress

Intel

®

IXP2800

Network Processor

Framing/MAC

Device

(PHY)

SPI-4

Protocol

RDAT

Receive protocol is SPI-4

Transmit mode is CSIX

TDAT

Egress

Intel IXP2800

Network Processor

TSTAT

Flow Control

Receive protocol is CSIX

Transmit mode is SPI-4

RDAT

Optional

Gasket

(Note

1

)

Switch

Fabric

CSIX

Protocol

RSTAT

TDAT

Notes:

1. Gasket is used to convert 16-bit, dual-data Intel IXP2800 Network Processor signals to wider

single edge CWord signals used by Switch Fabric, if required.

2. Per the CSIX specification, the terms "egress" and ingress" are with respect to the Switch Fabric.

So the egress processor handles traffic received from the Switch Fabric and the ingress

processor handles traffic sent to the Switch Fabric.