Hardware Reference Manual 55

Intel

®

IXP2800 Network Processor

Technical Description

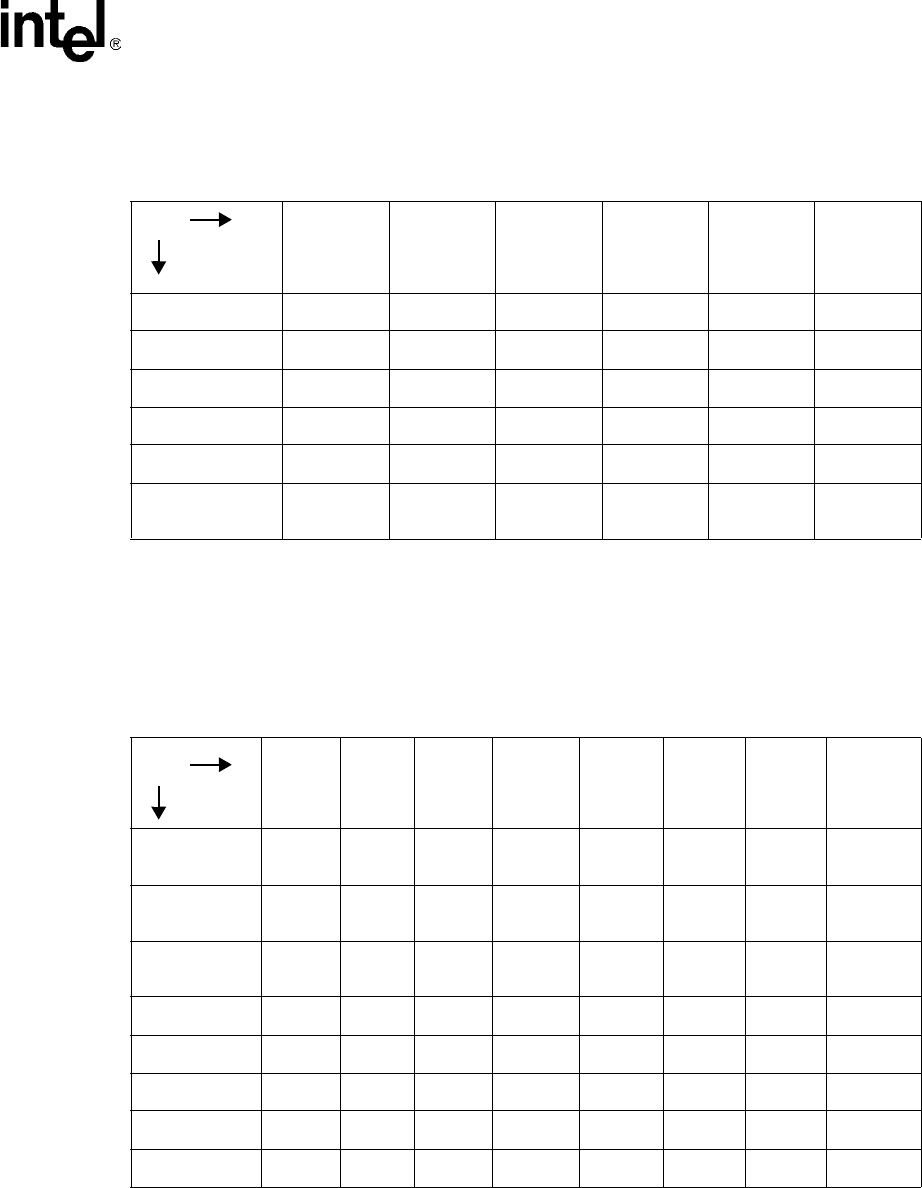

Verification is required to test only the order rules shown in Table 12 and Table 13).

Note: A blank entry in Table 12 means that no order is enforced.

Table 13 shows the architectural guarantees of order to access to the SAME SRAM Q_array entry

between a reference of any given type (shown in the column labels) and a subsequent reference of

any given type (shown in the row labels). The definition of first and second is defined by the order

they are received by the SRAM controller. The same caveats apply as for Table 12.

Table 12. Address Reference Order

1

st

ref

2

nd

ref Memory

Read

CSR Read

Memory

Write

CSR Write

Memory

RMW

Queue /

Ring /

Q_Descr

Commands

Memory Read Order

CSR Read Order

Memory Write Order

CSR Write Order

Memory RMW Order

Queue / Ring / Q_

Descr Commands

See

Table 13.

Table 13. Q_array Entry Reference Order

1

st

ref

2

nd

ref

Read_Q

_Descr

head,

tail

Read_

Q_Des

cr

other

Write_Q

_Descr

Enqueue Dequeue Put Get Journal

Read_Q_Descr

head,tail

Order

Read_Q_

Descr other

Order

Write_Q_

Descr

Enqueue Order Order Order

Dequeue Order Order Order

Put Order

Get Order

Journal Order