148 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

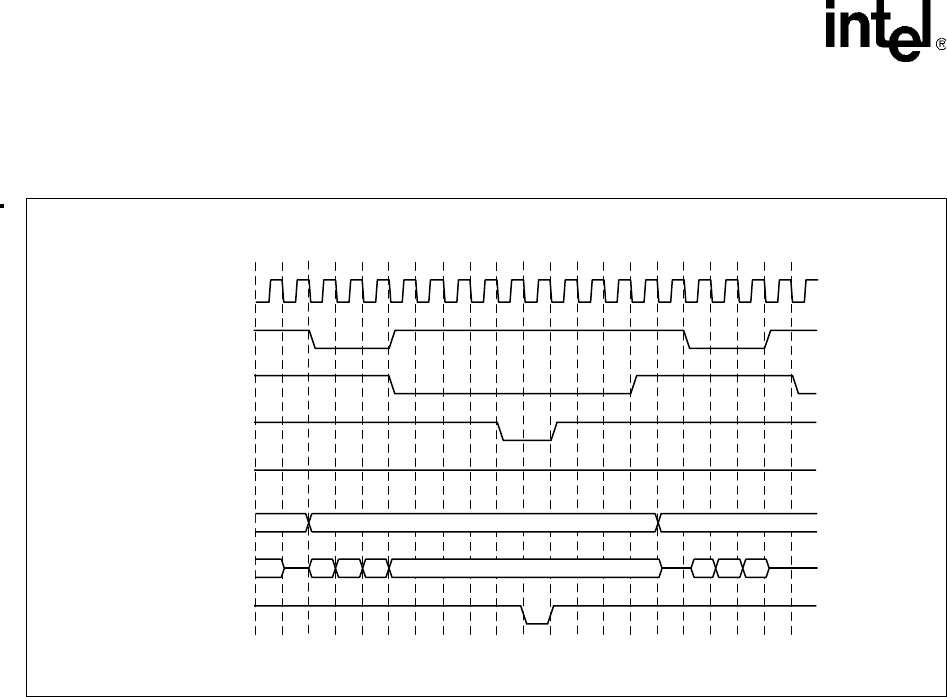

3.12.7.6.2 Mode 0 Single Write Transfer for Self-Timing Device

Figure 39 depicts the single write transfer for a self-timing device with the CSR programmed to

setup=4, pulse width=0, and hold=3. Similarly, a read transaction is attached behind.

Similar to the single write for fixed-timed device, the ALE_L, CS_L[1:0], AD[7:0], and A[1:0]

follow the same pattern, and the timing is controlled by the timing control register — except for the

WR_L, which is terminated depending on the SP_ACK_L returned from the self-timing device.

The time-out counter will be set to 255. If no SP_ACK_L responds back when the time-out counter

reaches 0, the transaction is terminated with a time-out. An interrupt signal is issued to the bus

master simultaneously with the time-out register update.

Figure 39. Mode 0 Single Write Transfer for a Self-Timing Device

A9707-03

SP_CLK

SP_ALE_L

SP_CS_L

[1:0]

SP_WR_L

D[7:0]

A[1:0]

24:1817:109:2 24:1817:109:2

SP_RD_L

SP_A[1:0]

SP_AD[7:0]

SP_ACK_L

20 4 6 8 10 12 14 16 18 20