Hardware Reference Manual 89

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

The instruction cache is virtually addressed and virtually tagged. The virtual address presented to

the instruction cache may be remapped by the PID register.

3.4.1 Instruction Cache Operation

3.4.1.1 Operation when Instruction Cache is Enabled

When the cache is enabled, it compares every instruction request address to the addresses of

instructions that it is holding in cache. If the requested instruction is found, the access “hits” the

cache, which returns the requested instruction. If the instruction is not found, the access “misses”

the cache, which requests a fetch from external memory of the 8-word line (32 bytes) that contains

the instruction (using the fetch policy). As the fetch returns instructions to the cache, they are put in

one of two fetch buffers and the requested instruction is delivered to the instruction decoder. A

fetched line is written into the cache if it is cacheable (code is cacheable if the MMU is disabled or

if the MMU is enabled and the cacheable (C) bit is set to 1 in its corresponding page).

Note: An instruction fetch may “miss” the cache but “hit” one of the fetch buffers. If this happens, the

requested instruction is delivered to the instruction decoder in the same manner as a cache “hit.”

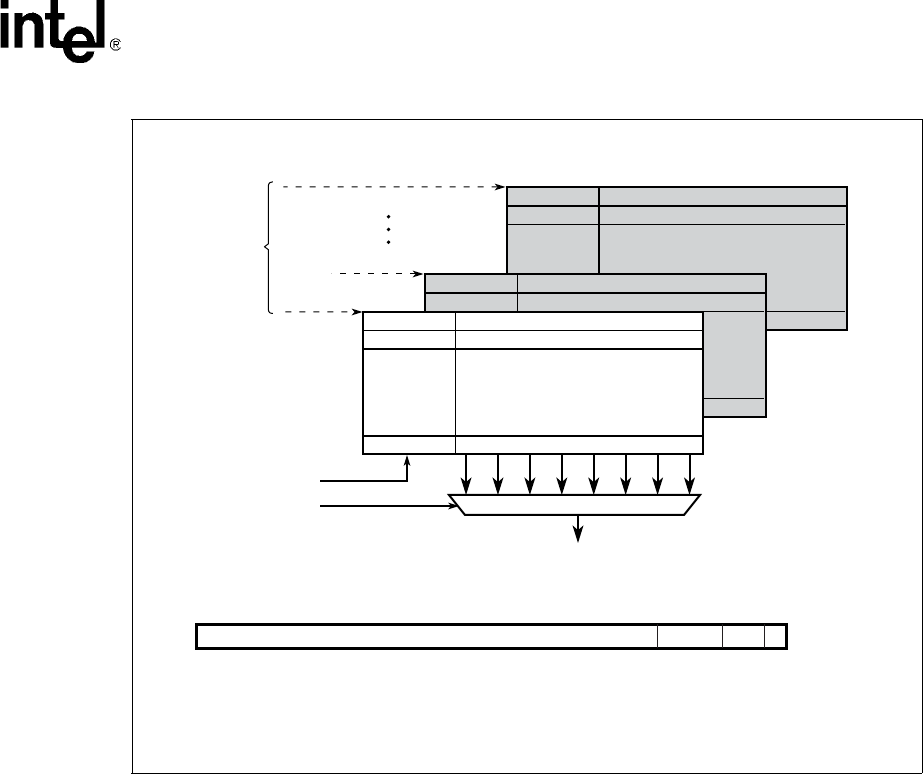

Figure 18. Instruction Cache Organization

A9685-01

8 Words (cache line)

DataCAM

Tag

Instruction Address (Virtual)

Note: CAM = Content Addressable Memory

Set Index

Word Select

Instruction Word

(4 bytes)

Word

way 0

Set 31

Set 1

way 1

31 54 21010 9

8 Words (cache line)

DataCAM

way 0

way 1

Set 0

8 Words (cache line)

DataCAM

way 0

way 1

way 31

Tag

This example

shows Set 0 being

selected by the

Set Index

Set Index