Hardware Reference Manual 43

Intel

®

IXP2800 Network Processor

Technical Description

2.3.6 Local CSRs

Local Control and Status registers (CSRs) are external to the Execution Datapath, and hold specific

data. They can be read and written by special instructions (local_csr_rd and local_csr_wr) and are

accessed less frequently than datapath registers.

Because Local CSRs are not built in the datapath, there is a write-to-use delay of three instructions,

and a read-to-consume penalty of two instructions.

2.3.7 Execution Datapath

The Execution Datapath can take one or two operands, perform an operation, and optionally write

back a result. The sources and destinations can be GPRs, Transfer registers, Next Neighbor

registers, and Local Memory. The operations are shifts, add/subtract, logicals, multiply, byte align,

and find first one bit.

2.3.7.1 Byte Align

The datapath provides a mechanism to move data from source register(s) to any destination

register(s) with byte aligning. Byte aligning takes four consecutive bytes from two concatenated

values (8 bytes), starting at any of four byte boundaries (0, 1, 2, 3), and based on the endian-type

(which is defined in the instruction opcode), as shown in Example 5. The four bytes are taken from

two concatenated values. Four bytes are always supplied from a temporary register that always

holds the A or B operand from the previous cycle, and the other four bytes from the B or A operand

of the Byte Align instruction.

The operation is described below, using the block diagram in Figure 6. The alignment is controlled

by the two LSBs of the BYTE_INDEX Local CSR.

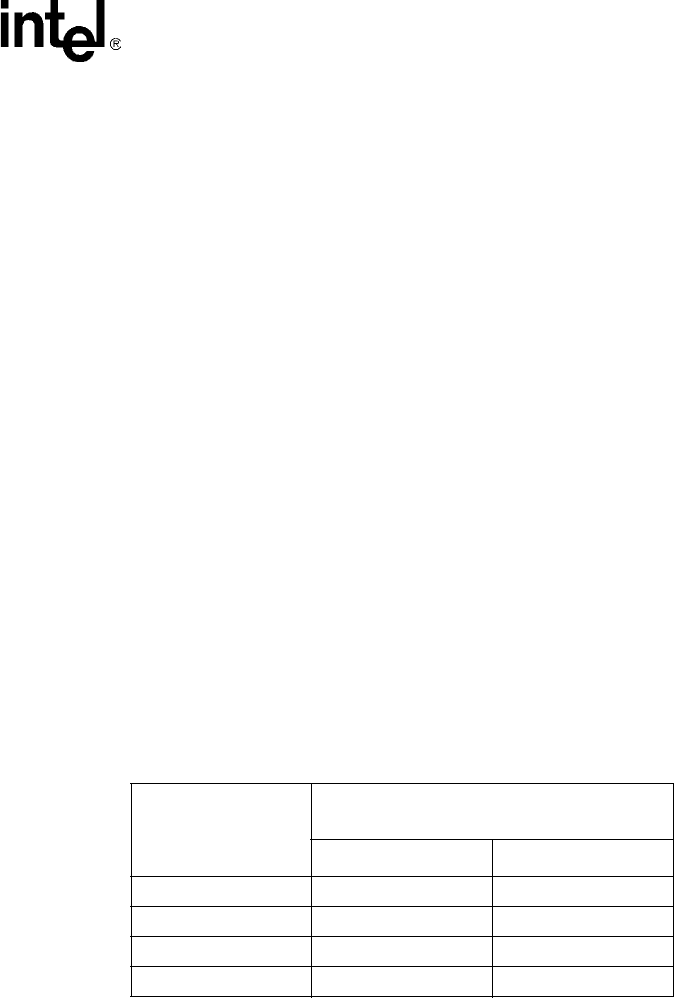

Table 6. Align Value and Shift Amount

Align Value

(in Byte_Index[1:0])

Right Shift Amount (Number of Bits)

(Decimal)

Little-Endian Big-Endian

0032

1824

21616

3248