270 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

Note: A Dead Cycle is any cycle after the end of a CFrame, and prior to the start of another CFrame

(i.e., SOF is not asserted). The end of a CFrame is defined as after the Vertical Parity has been

transmitted. This in turn is found by counting the Payload Bytes specified in the Base Header and

rounding up to CWord size.

After an element has been sent on the transmit pins, the valid bit for that element is cleared. The

Tx_Sequence register is incremented when the element has been transmitted; by also maintaining

a sequence number of elements that have been allocated (in software), the microcode can

determine how many elements are in-flight.

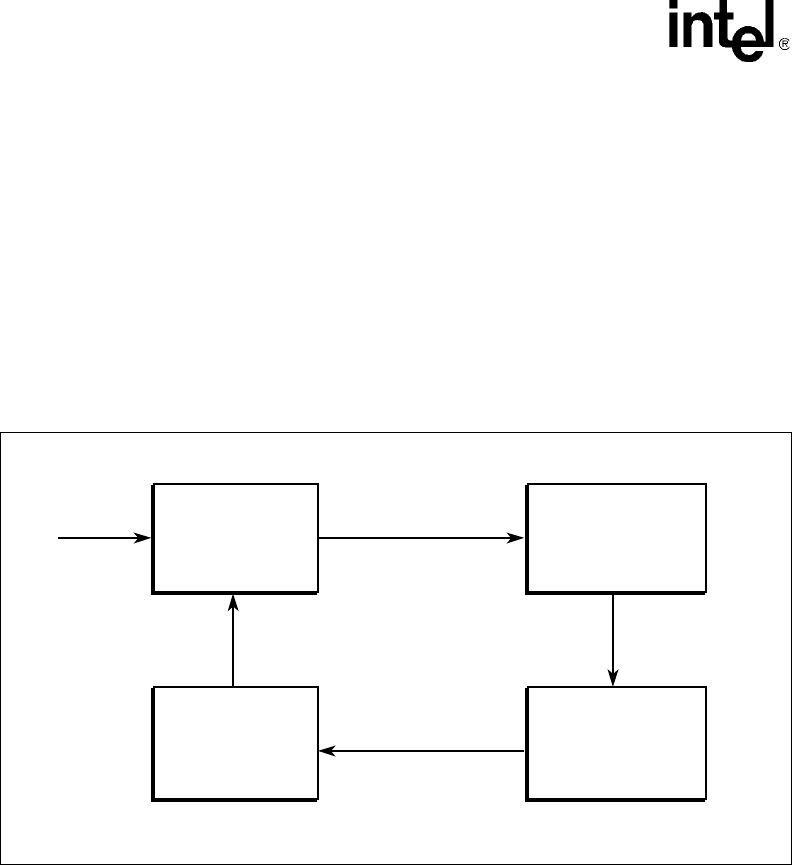

8.3.3.3 Transmit Summary

The states that a TBUF element goes through (Free, Allocated, Transmitting, and Valid) are shown

in Figure 95.

8.3.4 Transmit Flow Control Status

Transmit Flow Control is handled partly by hardware and partly by software. Information from the

Egress IXP2800 Network Processor can be transmitted to the Ingress IXP2800 Network Processor

(as described in Section 8.2.7 on Receive Flow Control); how it is used is described in the

remainder of this section.

Figure 95. TBUF State Diagram

A9344-02

Free. Element is empty

and available to be

allocated to be filled.

Allocate new element

(Next element is kept by

ME software)

Set valid by

msf[write]

All data in element

transmitted

Transmitting. Data in

element is being sent

out on Tx pins.

All previous elements

transmitted

Reset

Allocated. Element is

being filled with data

under ME control. There

is no limit to how many

elements may be in this

state.

Valid. Element has been

set valid by ME code

using one of two methods.

In this state, it will wait to

be transmitted (FIFO

order is maintained).