330 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

PCI Unit

9.2.11 PCI Central Functions

The CFG_RSTDIR pin is active high for enabling the PCI Unit central function.

The CFG_PCI_ARB(GPIO[2]) pin is the strap pin for the internal arbiter. When this strap pin is

high during reset then the XPI Unit owns the arbitration.

The CFG_PCI_BOOT_HOST(GPIO[1]) pin is the strap pin for the PCI host.When

PCI_BOOT_HOST is asserted during reset then PCI Unit will support as a PCI host.

Note * CFG_PCI_RSTDIR = 1 then central function.

* CFG_PCI_BOOT_HOST must be central function.

* CFG_PCI_ARB must be central function.

9.2.11.1 PCI Interrupt Inputs

The PCI Unit supports two interrupt lines from the PCI Bus as host. One of the interrupt lines will

be open-drain output and input. The other interrupt line will be selected as PCI interrupt input.

Both the interrupt lines can be enabled in the Intel XScale

®

core Interrupt Enable register.

9.2.11.2 PCI Reset Output

If the IXP2800 Network Processor is central function (CFG_RSTDIR =1), PCI Unit will be

asserting the PCI_RST_L after the system power-on. The Intel XScale

®

core has to write to the

PCI External Reset bit in the IXP2800 Network Processor’s Reset register to de-assert the

PCI_RST_L. In this case, chip reset CLK_NRESET) is driven by a signal other than PCI_RST_L.

When the PCI Unit is not configured as the central function (CFG_RSTDIR =0), PCI_RST_L is

used as a chip reset input.

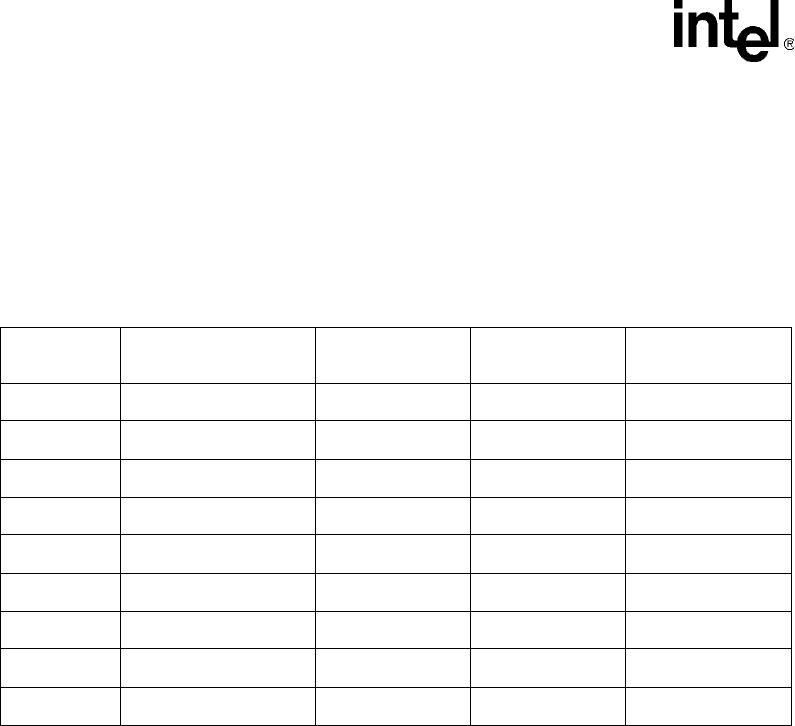

Table 122. Legal Combinations of the Strap Pin Options

CFG_PCI_BOOT_HOST

(GPIO[1])

CFG_PCI_ARB

(GPIO[2])

CFG_PCI_RSTDIR

(Central function)

CFG_PROM_BOOT

(GPIO[0])

OK 0 0 0 0

OK 0 0 0 1

OK 0 0 1 1

Not supported 0 1 0 x

OK 0 1 1 1

Not supported 1 0 0 x

OK 1 0 1 1

Not supported 1 1 0 x

OK 1 1 1 1