382 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Performance Monitor Unit

acknowledge signal (CAP_CSR_RD_RDY). When the data is returned, CAP puts the read data

into the Push Data FIFO, arbitrates for the S_Push_Bus, and then the Push/Pull Arbiter pushes the

data to the destination identified in PP_ID.

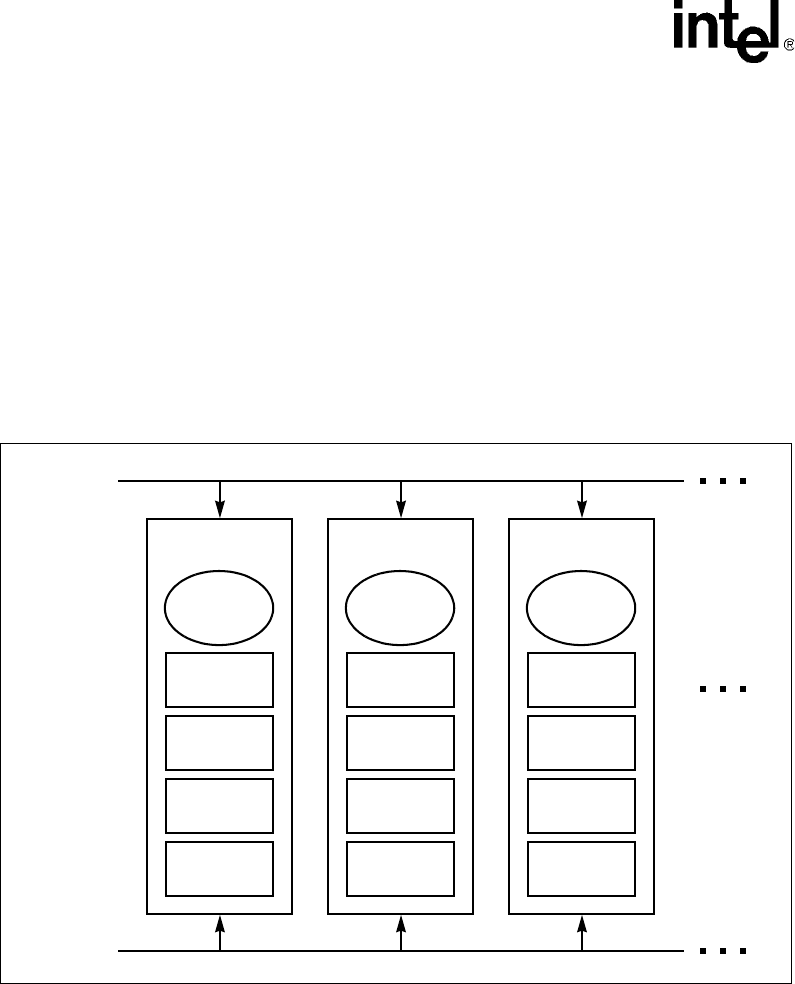

11.2.3 Configuration Registers

Because the CHAP unit resides on the APB, the offset associated with each of these registers is

relative to the Memory Base Address that the configuration software sets in the PMUADR register.

Each counter has one command, one event, one status, and one data register associated with it.

Each counter is “packaged” with these four registers in a “counter block”. Each implementation

selects the number of counters it will implement, and therefore how many counter blocks (or slices)

it will have. These registers are numbered 0 through N - 1 where N represents the number of

counters - 1. See Figure 140.

11.3 Performance Measurements

There are several measurements that can be made on each of the hardware blocks. These

measurements together would enable improvements in hardware and software implementation and

architectural issues. Table 152 describes the different blocks and their associated performance

measurement events.

Figure 140. Conceptual Diagram of Counter Array

Register

Interface

Counter

Block 0

Counter

Command

Register

Events

Register

Status

Register

Data

Register

Counter

Block 1

Counter

Command

Register

Events

Register

Status

Register

Data

Register

Counter

Block 2

Counter

Command

Register

Events

Register

Status

Register

Data

Register

Event

Signals