376 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Performance Monitor Unit

11.1.2 Motivation for Choosing CHAP Counters

The Chipset Hardware Architecture Performance (CHAP) counters enable statistics gathering of

internal hardware events in real-time. This implementation provides users with direct event

counting and timing for performance monitoring purposes, and provides enough visibility into the

internal architecture to perform utilization studies and workload characterization.

This implementation can also be used for chipset validation, higher-performing future chipsets, and

applications tuned to the current chipset. The goal is that this will benefit both internal and external

hardware and software development. The primary motivation for selecting the CHAP architecture

for use in the IXP2800 Network Processor product family is that it has been designed and validated

in several Intel desktop chipsets and the framework also provides a software suite that may be

reused with little modification.

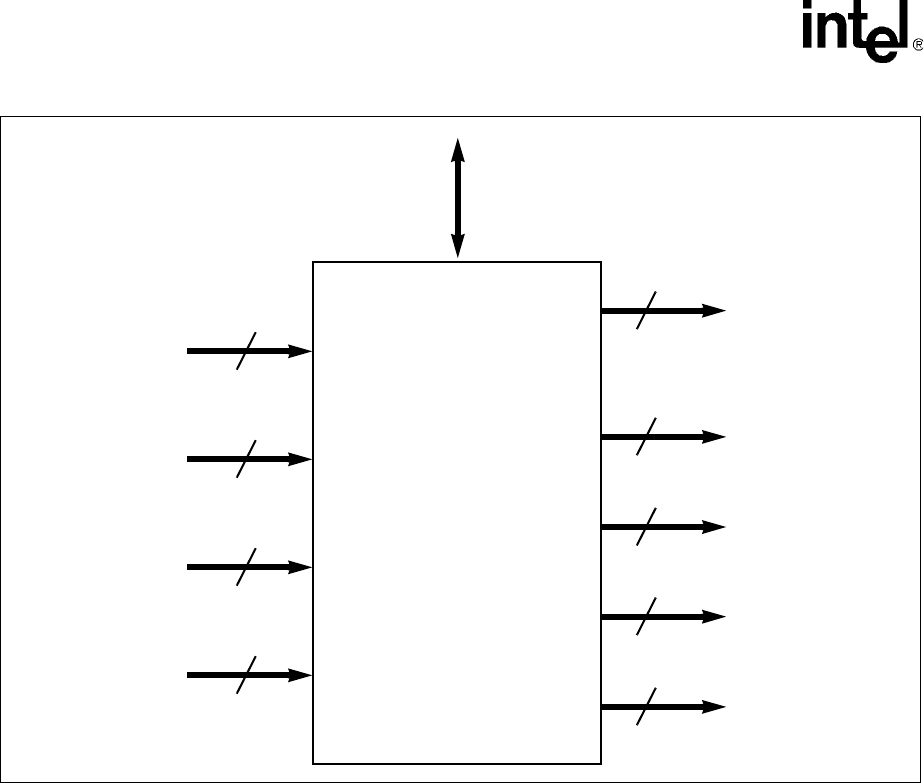

Figure 136. Performance Monitor Interface Block Diagram

Performance Monitoring

Unit

APB Bus for

Read/Write of

CHAP Registers

Status Conditions

for Interrupts from

CHAP Counter 0

Status Conditions

for Interrupts from

CHAP Counter 1

Status Conditions

for Interrupts from

CHAP Counter N-2

Status Conditions

for Interrupts from

CHAP Counter N-1

Event Multiplexer

Control to

Hardware Blocks

Events from

Hardware Block A

Events from

Hardware Block B

Events from

Hardware Block C

Events from

Hardware Block D