Hardware Reference Manual 175

Intel

®

IXP2800 Network Processor

Microengines

Example 24 shows an align sequence of instructions and the value of the various operands.

Table 59 shows the data in the registers for this example. The value in Byte_Index[1:0] CSR

(which controls the shift amount) for this example is 2.

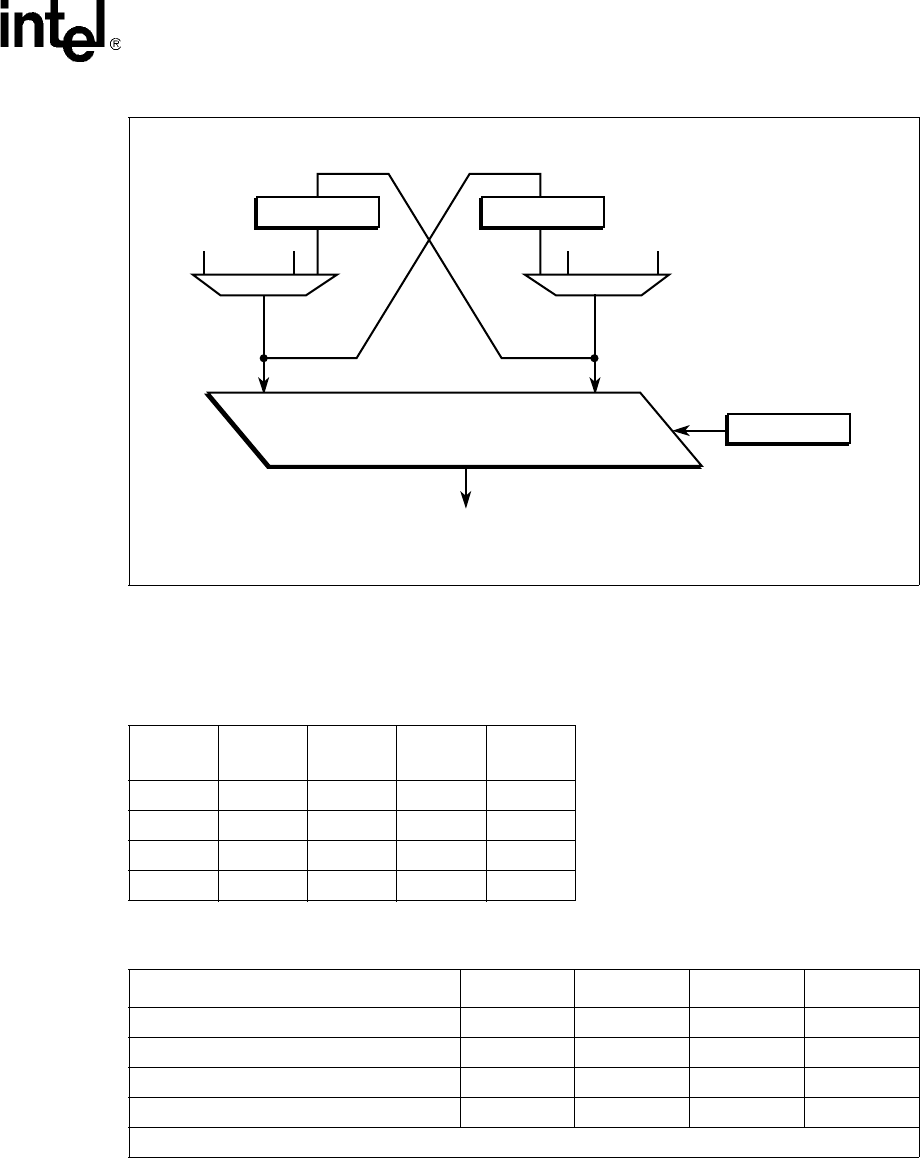

Figure 58. Byte Align Block Diagram

A9353-01

Prev_A

Byte_Index

Result

B_OperandA_Operand

Prev_B

. . .

. . .

Shift

Table 59. Register Contents for Example 23

Register

Byte 3

[31:24]

Byte 2

[23:16]

Byte 1

[15:8]

Byte 0

[7:0]

00123

14567

289AB

3CDEF

Example 24. Big-Endian Align

Instruction Prev B A Operand B Operand Result

Byte_align_be[--, r0] -- -- 0123 --

Byte_align_be[dest1, r1] 0123 0123 4567 2345

Byte_align_be[dest2, r2] 4567 4567 89AB 6789

Byte_align_be[dest3, r3] 89AB 89AB CDEF ABCD

NOTE: A Operand comes from Prev_B register during byte_align_be instructions.